4月17日~19日にかけて横浜で開催されたCOOL Chips 22のトップバッターは、富士通のドメインスペシフィックコンピューティングに関する丸山拓巳氏の発表であった。

良く知られているように、ムーアの法則は終わりに近づき、半導体のプロセス技術だけでは大きな性能改善は難しくなってきている。このため、ドメインスペシフィックコンピューティングに注目が集まっている。

ドメインスペシフィックコンピューティングでは、汎用性を犠牲にして、コンピュータを特定分野向けに設計することにより、高い性能を実現しようとする。次の図のように、汎用コンピューティングやスーパーコンピューティングは、分野を限定せず広い用途に使えるが、性能がそれほど高くはできない。

しかし、推論(Inference)専用のハードウェアや学習(Deep Learning)専用のハードウェアを作れば、同じトランジスタ数を使う汎用コンピュータよりも性能の高いものが作れる。また、DAと書いてあるのは、これから述べるデジタルアニーラであり、組み合わせ最適化問題専用のハードウェアである。

より、エキゾチックなのは量子コンピューティングや脳をまねるブレインコンピューティングなどがある。これらは大きな可能性があるが、実用化はまだまだ先のことであり、今回の講演の範囲外である。

-

ドメインスペシフィックコンピューティングは、ハードウェアを特定分野向けに最適化することにより高性能化を目指すアプローチである。富士通は組み合わせ問題専用のデジタルアニーラとディープラーニング用のDLUを開発している (このレポートの図は、COOL Chips 22における丸山氏の発表資料のコピーである)

組み合わせ最適化問題を解くデジタルアニーラ

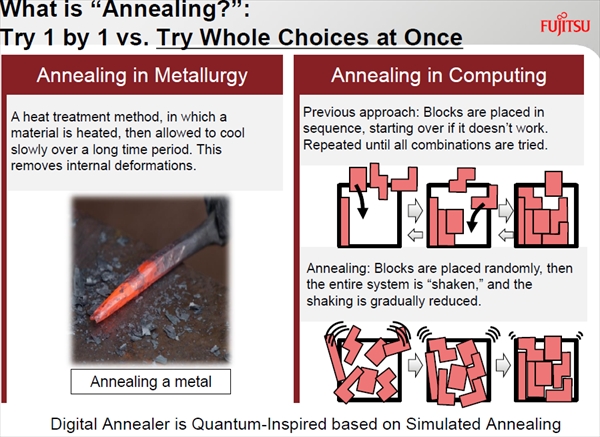

アニーリングは焼きなましという処理で、金属を高温に熱してから徐々に冷却していく。金属の切削加工などで生じた歪みなどを取り除き、柔らかく加工しやすくすることができる。次の図のように、高温状態では熱エネルギーが大きく、それぞれの分子などがバラバラになっているが、温度が下がるとだんだんと整列してエネルギーが低い状態に落ち着いていく。

これをコンピュータの計算で行うのがシミュレーテッドアニーリングで、最低エネルギーの状態が最適解になるように問題を定式化して組み合わせ問題を解く方法として使われている。このシミュレ―テッドアニーリングを量子的に行う方法を東工大の西森教授が提案し、カナダのD-Wave社はこの原理に基づく量子アニーリングマシンを発売している。

物質のエネルギー状態は複雑で、冷却していけば最低のエネルギー状態に落ち着くとは限らず、グローバルな最低よりもエネルギーの大きなローカルミニマムで止まってしまうことも多い。量子アニーリングを使うと、ローカルミニマムに捕らえられても周囲のエネルギーの高い山を量子トンネル効果で突き抜けて移動できるので、グローバルの最低エネルギーを見付けやすくなるが、通常のシミュレーテッドアニーリングでも、やり方によってかなり良い解が得られるようである。

運転時間を最短にする荷物の配送順序を探す問題などでは、本当の最短ルートが見つからなくても、それに近いルートが分かれば良いというケースも多い。このようなケースでは厳密なエネルギー最小の解でなくても十分役に立つ。

従来の方法では、ピースを順番に入れてどれだけ詰まって低いエネルギー状態になるかを見ていたが、富士通はランダムにピースを入れ、全体をゆすって詰め込むという方法を使っている。このゆすり込みは乱数で、いったん系のエネルギーを上げてからまた冷やすことで実現している。

-

アニーリング(焼きなまし)は高温状態から徐冷することで歪みを除去する。これを組み合わせ問題の最適解を求めるために使うのがシミュレ―テッドアニーリング。従来はピースを順番に入れていって最低エネルギーの解が得られるまで繰り返していたが、富士通は、全部をいれておいてからゆすり込んで、詰め込みを図るという方法を採用している

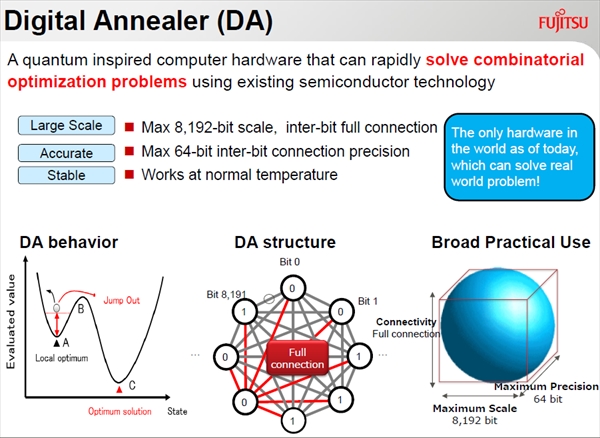

量子アニーリングは収束性は高いが、超伝導素子を使うため、超低温にする必要がある。しかし、デジタルアニーラは、普通のCMOS回路であるので常温で使えるというメリットがある。

富士通のデジタルアニーラは、8192bitの選択肢を持ち、全対全結合になっている。そして、64bitの精度で評価関数の計算ができる。この計算は通常のコンピュータでもできるが、DAチップはこの部分をハードウェア化しているので、並列計算ができ、通常のコンピュータで計算するよりずっと高速に処理することができる。

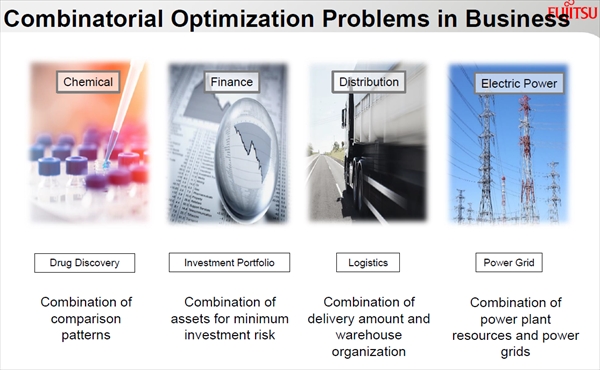

組み合わせ最適化問題は、創薬の分野では条件のパターンの組み合わせ問題、投資の分野では投資ポートフォリオのリスクの最小化、運送の分野では運送順序の最適化、電力供給の分野では発、送電網の最適化など多くの問題に適用できる。