英Armは12月18日(現地時間)、自動車向けのアプリケーションプロセッサIPとして、「Cortex-A65AE」を発表した。

Cortex-A65AEは、Helios-AEとして説明されているもので、Cortex-A53の後継となる(Photo01)。

以前の記事でも紹介したが、HeliosはCortexシリーズとしては初の「モバイルを対象としない」IPである。

元々はインフラストラクチャ向けであるNeoverse用に開発されたもので、これのオートモーティブ(自動車)向けがHelios-AEとなる形だ。

この中身の話は後で説明するとして、まずは位置づけについて。Armによれば、Cortex-A65AEは例えばセンサフュージョンにおけるハブなどの、フロントエンド向けのプロセッサという位置づけにある(Photo02)。

Sensor Fusionの場合、I/O処理が多いため必ずしも突出した処理性能は必要なく、むしろバランス良いコアが求められる。逆に後段になるほど処理性能が必要とされるため、こちらはCortex-A76AEが担うという形だ(Photo03)。

またドライバ・アシスタントレベルで言えばCortex-A65AEにMali-C71(自動車向けISP)で実装できる。最近はLevel 1/2の自動運転機能が高級車のみならず普及車とか軽自動車にまで広がりつつあるが、こうしたエントリ向けにはCortex-A65AEが最適とする(Photo04)。

さらにIVIやデジタルコックピットなどに向けてもCortex-A65AEは利用可能としている(Photo05)。こちらは、特にアクセラレータと組み合わせて高いスループットを利用できる点がメリット、としている。

-

Photo05:こちらはCortex-A76と組み合わせてLock-Stepの環境でbig.LITTLEを構成可能に出来る点がメリットとなるだろう(Cortex-A53だとLock-Stepが構成できない)

さてそのCortex-A65AEであるが、現時点ではまだパイプライン構成などは明らかにされていない。ただし主要な特徴として

- Super Scalar、Out-of-Order構成

- Cortex-Aシリーズとして初めてのSMT(Simultaneous Multi-Threading)構成。1コアあたり2Threadをサポート

- 命令セットはArm v8.2A相当。ただしv8.3AのLDAPR命令がサポートされている。v8.4Aの命令については未サポートの模様。またサポートされるISAはA64(64bit命令)のみで、32bitおよびThumb2については未サポート

- 1クラスタあたり、最大8コア構成(Thread数で言えば最大16Thread)

- 自動車向け機能としてRAS機能、およびSplit-Lock機能を搭載し、さらにDCLS(Dual Core Lock-Step)にも対応。ISO26262 ASIL-Dに準拠可能

などが挙げられている(Photo06)。

ちなみにターゲットプロセスは(Photo01にもあるように)7nmとされ、パフォーマンスデータとしてはCortex-A53比で

- コアあたりのパフォーマンスは整数演算の場合で70%アップ

- 自動車向けアプリケーション利用時のメモリスループットが3.5倍

- ACPポート経由でのアクセラレータからの読み出しスループットは6倍以上

といった数字が示されている。

ただこちらは比較の環境が不明(Cortex-A53のターゲットプロセスや動作周波数を一致させての比較かどうかが判らない)なため、単純に数値は鵜呑みにしにくい。とはいえCortex-A53はIn-Orderで完全2命令のSuper-Scalar構成であり、なので仮にCortex-A65AEが3命令のOut-of-Order構成なら、70%の性能改善と言われても納得できるものはある。

また命令セットのところで列挙したが、Cortex-A65AEはCortex-Aシリーズとしては初めて、32bit命令をサポートしない、純粋に64bitのプロセッサとなる。自動車向け、あるいはインフラストラクチャ向けであれば32bitのサポートは無くても良い、という判断だったと思われる。これがモバイル向けや組み込み向けにHeliosコアが提供されない理由であり、SMTのサポートと併せて「ユニークなコア」である理由と思われる。

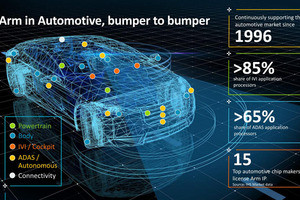

ちなみに本件とは直接関係ないが、Cortex-A65AEの発表前日の12月17日、ArmはAutomotiveおよびEmbeddedを統括するSenior VPとして、元はIntelでIoT Groupを率いていたDipti Vachani氏が就任した事を発表している。このところのArmのオートモーティブへの力の入れ方が凄い事を思わせる話だが、Heliosがインフラよりも先にオートモーティブに投入されるのも、このあたりの事情が関係しているのかもしれない。