10月1日よりサンノゼのFairmont HotelでXDF(Xilinx Developer Forum) 2018が開催されているが、このXDFの初日、Armが新しく「DesignStartプログラム」をXilinxのFPGAを対象にスタートすることが発表された(Photo01)。

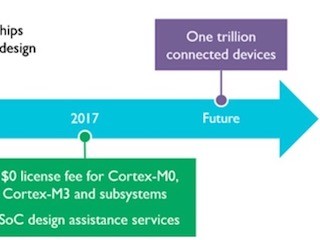

ArmのDesignStartは2010年にスタートした。当初は非営利あるいは教育機関向けにCortex-M0を無償で利用できるというものだったが、その後プログラムの内容はどんどん強化され、昨年にはCortex-M3コアの利用も可能になっており、小規模の開発に際しては初期ライセンス費用が免除されることで、Cortex-M0/M3を導入しやすくするというものとなった(Photo02)。

-

Photo02:昨年1年だけで3000以上もこれが利用され、うち300あまりが商用ライセンスに移行したとする。不幸にもプロジェクトが上手くいかない場合にArmにライセンス費用を支払う必要がないので、(相対的に)気軽に利用できるのがDesignStartのメリットである,2017年だけで3000以上が利用

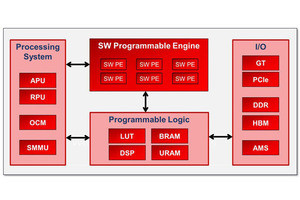

今回発表のDesignStartプログラムの強化はこの延長にあるもので、XilinxからCortex-M1およびCortex-M3のSoft IPが提供され、これを利用してFPGAベースでシステムを構築する場合、Armへのライセンスおよびロイヤリティの支払いが不要、というものである(Photo03)。

これを利用して、迅速にFPGAベースでアプリケーションを開発できるとしている(Photo04)。

-

Photo04:何気なく書いてあるが、利用にはVivadoが必要と言うことで、たとえばSpartan 6+ISEの環境では使えない(Spartan 6そのものは利用可能)というあたりが一応制限といえば制限である

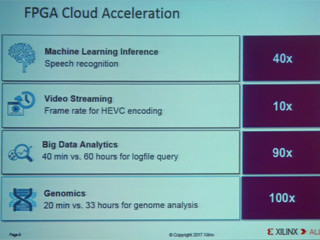

なぜ、こうした取り組みに踏み切ったのか? という背景がPhoto05だ。

-

Photo05:FPGAをベースとしたシステムが7億台に達するという見込み予想はなかなか凄いが、これがもしRISC-Vベースで構築されたりすると、Armのエコシステムに大打撃になりかねない。これを防ぐためには同様に無償で提供することが必要、という判断だと思われる

日本などでもそうだが、最近はASICやASSPを利用する代わりにFPGAで、という動きが高まっており、これは別にアプリケーションプロセッサだけではなくMCUを利用するようなケースでも同じである(Photo06)。

このトレンドをキャッチアップするためにDesignStartプログラムを強化した、というのがArmからの表向きの説明である。では、裏向きは? というと、おそらくはRISC-Vへの対抗ということが挙げられる。Microsemiなどは積極的にRISC-Vを同社のFPGA向けに用意しており、こちらも無償で利用ができる。ArmとしてはFPGA向けのIPを有償提供することで、RISC-Vにマーケットシェアを奪われるよりは、無償でIPを提供することで、ソフトウェアの一貫性をアピールする(Photo06)と共に、膨大なすでに利用されている実績を強くアピールする(Photo07)ことで自社のエコシステムを維持していく考えと思われる。

すでにCortex-M1のダウンロードは開始しており、開発環境に加えてすぐ利用できるハードウェアも用意されている(Photo08)。

またこのDesignStartの対象製品は(Vivadoがサポートする)FPGAすべてとのころで、それこそSpartan 6やVirtex-6とかでも利用できる(ただし冒頭に書いたとおりISEは未サポート)とのことだ。また実装する個数にも制限は無い(ただしシステムとのインターコネクトに限界がある)そうで、なので複数のCortex-M1/M3プロセッサを1つのFPGA上で動かすことも可能という話であった(Photo09)。

-

Photo09:Thumb-2ベースのアプリケーションであれば、Soft IPのCortex-M1/M3でも良いし、より上位のZYNQのHard IPのCortex-A/Rを使って高速に動作させることもできる、とする。しいて言えばCortex-M1がArm v6M、Cortex-M3がArm v7Mというあたりがちょっと面倒かもしれないが

ちなみにこのDesignStartプログラム、今のところXilinxのみをサポートするそうで、他のFPGAベンダに関しては「今のところ予定は無い」との事。またCortex-M3はともかくCortex-M1に関しては、当初発表時にXilinx、Altera(現Intel)、Actel(現Microchip。2018年にActelを買収したMicrosemiを買収)の3社のFPGAでそのまま無償で利用できるという話であったため、これに基づくCortex-M1のコアは現在も有効だと思うとArmではしつつ、この時のCortex-M1 IPと今回のDesignStartプログラム強化に基づくIPはまったくビジネスモデルが異なるので、同列に考えてはいけないという説明であった。

このDesignStart FPGA、すでに専用WebサイトにてCortex-M1 IPの提供が開始されており、Cortex-M3コアも2018年11月から提供が開始される予定である。