SRAM代替を狙う組み込みMRAMプロセスに対応するFD-SOI

また、今回のSFFでは3本の基調講演が行われたのだが、その3本目にCIES(東北大学国際集積エレクトロニクス研究開発センター)の遠藤哲郎センター長(兼 東北大学大学院 教授)が登壇。MRAMに関する講演が行われた。内容を簡単に説明すれば、STT-MRAMをDRAMやSRAMの代わりにすることで、より省電力化を図りやすくなるという話であるのだが、SamsungはこのMRAMをFD-SOIの大きな武器にしようとしている(このあたりは同じくMRAMを前面に出しているGlobalfoundriesも同様)。

実はこれに関し、2018年6月に英Armは28FDS向けのeMRAM Compiler IPの提供を開始した事を発表している。要するにSamsungの28FDSを利用すると、MCUなどではSRAMと同じようにMRAMを扱えるという訳である。また28FDSは原理的にRFに強いということもあり、まずは5GのRF向けにデザインを獲得したいという意向を持っており、このRFとeMRAMでFD-SOIをもっと広げていきたいようだ。

難しいのは、Globalfoundriesも同じストーリーで22FDXや12FDXといったプロセスを前面に押し出していることで、これとTSMCの28nm系(28ULPなど)が真っ向勝負という事になりそうだ。

IPの拡充やパッケージング技術にも注力

このほか同社はパッケージングにもいろいろな技術を用意している(Photo08)。FOPLP-PoPはMobile SoC向けに、I-CubeはHPC向けにすでに実績がある技術だが、目新しい話題としては3D SiPを2019年に実用化するというアナウンスがあった。実はSamsung、DDR4 3DS(3D Stacking:DDR4ダイ同士をTSVで積層)チップを最初に量産し始めたメーカーでもあり、TSVに関する知見はだいぶ蓄積されているとは思うのだが、DRAMではなくロジックチップ向けのオプションとしてTSVを利用する最初のファウンドリということになる訳だ。

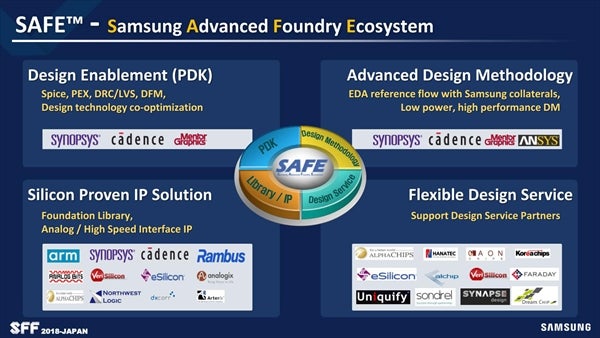

こうしたSamsung Foundryのさまざまな製造オプションやIPをサポートするのがSAFE(Samsung Advanced Foundry Ecosystem)である(Photo09)。PDKやEDA Tool、IP、そしてデザインサービスといった、ファウンドリを利用する際に必要となるさまざまな要素をSAFEでまとめて提供しようというものである。このあたりは当然歴史の長いTSMCに一日の長があるのは致し方ないところで、今後どこまでこの分野を充実させられるかはPure-play Foundryにとって重要な部分となってゆくだろう。

-

Photo09:ちょっと古い話だが、2012年頃にSamsungは別の「SAFE(SAmsung For Enterprise)」という、企業向けモバイル機器のプラットフォームを立ち上げており、同じ名称を使うのはどうだろう? という気はしなくもない

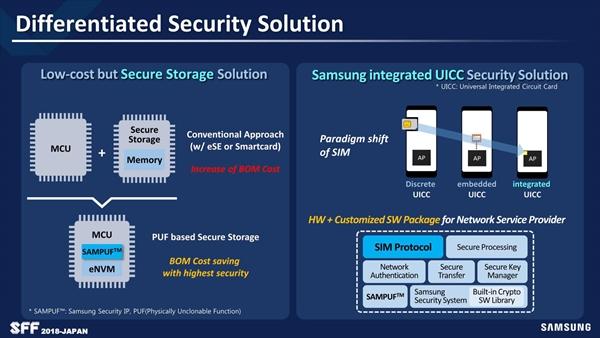

ちなみにセキュリティ分野での同社のソリューションとして提供されるのが、「Secure Storage」や「Integrated UICC」とされる(Phto10)。先般、ArmのPerion IoT Platformの発表があったが、例えばそこで提示された図でも右端にはDevice-to-data securityという文言が踊っている。通信に関してはMbed TLSや暗号化で対応するとして、デバイスそのもののセキュリティの強化は機器ベンダの仕事になるわけで、こうした事柄への対応のソリューションもきちんと提供できる、というアピールと考えれば良いだろう。

-

Photo10:PUFは"Physical Unclonable Function"の意味で、同社の「eSE」の1つとして提供される。UICCの統合は、秘匿性の強化とコストダウンの両面で効果がある

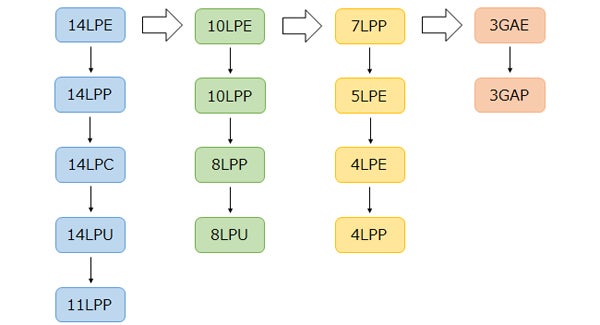

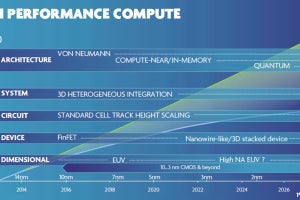

最後にそんなわけでSamsungの提供する先端プロセスをまとめてみたのが図1である(FD-SOIは除く)。14nm世代が意外に長く、これはLong Lived Nodeになるという以前の話を裏付けることになったが、10nm(今回追加された8LPU)も、これまた結構長い寿命になることが見えてきた。そもそも10LPP→8LPPでは配線層(M2)の狭ピッチ化と高密度ライブラリの利用が主な変更点で、基本的には10nmのジオメトリを利用する形だが、8LPUでは構造そのものは8LPPと同じながら、トランジスタの改良で7nm世代に近いパフォーマンスを実現可能としている。EUVの導入に二の足を踏むカスタマ向けソリューションというべきものだろう。

ちなみに7LPPから5LPEは、ジオメトリは変化が無くライブラリの違いとされるが、単にTrack数を減らすだけでなく、Single Dummy Gate(セルの両端のDummy Gateをそれぞれのセルごとに持たせるのではなく、2つのセルの間に1本だけDummy Gateが置かれる)や、COAG(Contact Over Active Gate)に近いコンタクト配置、さらにセル内の配線の改良といった事も含まれる模様だ。昨年のSFFでは、これは6LPPとして説明されていたはずだが、これが5LPEに名前が変わった理由は不明である。

また昨年掲げられていた5LPPは消えて、代わりに4LPE/4LPPが投入されることになった。これは最初に述べたように、GAAを使わなくても性能改善が可能なめどが立ったからということで、おそらくは4LPPが昨年の4GAA相当の性能と思われる。

こうして提供プロセスをまとめて見てみると、なんというか異様にプロセスの種類が増えた結果として顧客としてはむしろ選択に困りそうという気もしなくはないが、その代わりに1つの世代にあれもこれも新技術を詰め込むのではなく、最小限の新機能に留めて確実に量産開始に持ち込むというスタンスは、冒頭の「To be the most trusted Foundry」に繋がるものなのだろう。

確かに新技術を大量に盛り込みながらも、さっぱり量産に掛かれないよりはずっとマシではある。どんどん難易度が上がりつつある先端プロセスのファウンドリサービスを行うためには、これ位慎重に進めていくのが確実なのかもしれない、と感じた話であった。