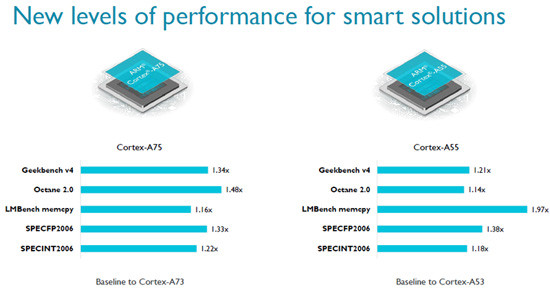

Cortex-A75は、各種ベンチマークで、A73と比較して1.16倍から1.48倍の性能を持っている。また、Cortex-A55は、A53と比較して1.18倍から1.97倍(ただし、memcpyを除くと1.18倍から1.38倍)の性能を持っている。

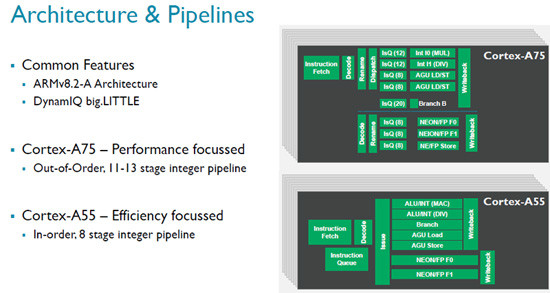

Cortex-A75とA55はARMv8.2-Aアーキテクチャであり、DynamIQ big.LITTLEをサポートしている。Cortex-A75は高性能にフォーカスしたプロセサコアで、Out-of-Orderの11-13段の整数パイプラインを持っている。一方、Cortex-A55は電力効率にフォーカスしたプロセサコアでインオーダの8段の整数パイプラインを使っている。

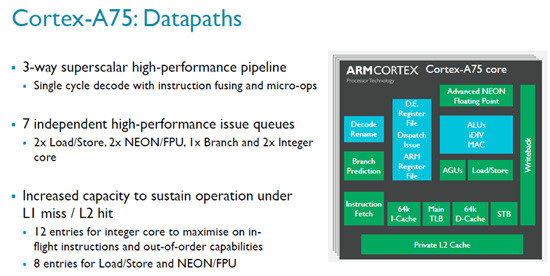

Cortex-A75は3wayのスーパスカラパイプラインで、2つのLoad/Store命令、2つのNEON/FPU命令、1つのBranch命令と2つの整数コア命令を発行する7つのイシューキューを持っている。また、A75は、L1キャッシュのミスをバッファに格納して後回しにして、後続のメモリアクセス命令を処理するが、このバッファを整数命令では12エントリ、NEON/FPU命令では8エントリに増量している。

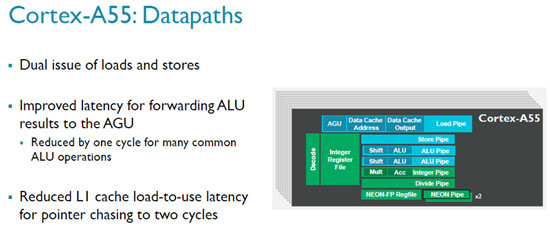

Cortex-A55のデータパスはA75と比べると簡単で、並列度という点ではLoadとStoreを並列に処理できるという程度である。しかし、A53と比べるとALUの計算結果をアドレス生成に回すのを含めて、多くの場合の整数演算のレーテンシを1サイクル短縮している。また、L1キャッシュのレーテンシを短縮し、ポインタを辿る時間を2サイクル短縮している。

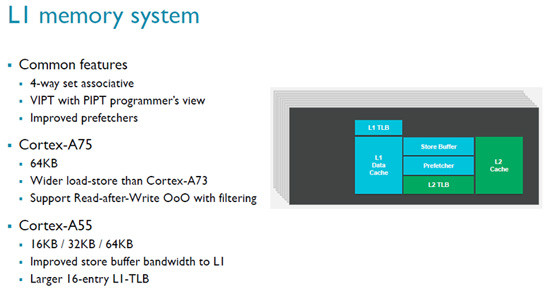

L1キャッシュは、Cortex-A75もA55も4wayで、VIPT(仮想アドレスでインデックスし、ヒットのチェックは物理アドレスのタグを使う)となっている。そして、前世代と比べるとプリフェッチャが改善されている。

Cortex-A75のL1キャッシュは64KBでロードストアのパスはA73より拡張されている。Cortex-A55のL1キャッシュはチップの設計時点で、16KB/32KB/64KBから選択することができる。

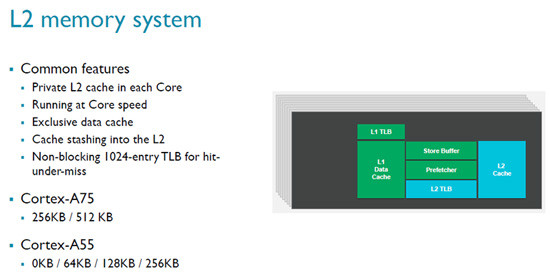

L2キャッシュは、Cortex-A75とA55ともにコアに1対1に対応するプライベートキャッシュとなっている。L2キャッシュはコアと同じクロックで動作する。このL2キャッシュはACPを経由して、アクセラレータやI/OからアクセスできるCache Stashingができるようになっている。

そして、L2キャッシュには1024エントリのノンブロッキングのTLBが付いている。L2キャッシュの容量は、A75は256KB/512KBで、A55は0KB/64KB/128KB/256KBから選択してチップに搭載できる。

A75/A55世代には取り入れられなかったが、次の世代では取入れを検討するのは次のような項目である。

- AI対応の内積の計算機構と半精度浮動小数点演算のサポート

- KVMの性能を改善するVirtualized Host Extensions

- マルチコアネットワーク性能を改善する」Cache stashingやアトミック処理

- ストレージクラスメモリのサポート

- 基幹サーバクラスのRAS

まとめであるが、2013年から2017年はコンピュートの性質が世の中を変えつつある時代である。このような時代にあって、ARMテクノロジを適用できる市場の拡張が重要である。DynamIQをサポートするCortex-A75は性能のブレークスルーを実現し、Cortex-A55はエネルギー効率が意味するものを再定義している。

工業的な用途や自動運転の場合は機能の安全性が重要になる。DynamIQのDSUや新しいキャッシュ機能などはマイクロアーキテクチャの能力を拡張している。と書かれている。

良くは分からないが、コンピュートの使われ方が広がってきているが、ARMはそれに対応していくということのようである。