ベースクラスタ部の構成では、ノード間のGPU同士のデータのやり取りは、GPUからCPUメモリにデータを転送し、CPUのPCI Expressポートに接続したIBアダプタを通り、スイッチを経由して相手方のIBアダプタに接続し、そこからPCI Expressを通って相手方のCPUのメモリにデータを送り、それから再びPCI Expressを通って相手方のGPUにデータを送るということになる。しかし、これは経路が長く通信レーテンシの点でも、消費電力の点でも無駄が多い。

筑波大はルネサス エレクトロニクスと共同で、「PEACH(PCI Express Adaptive Communication Hub)」というチップを開発している。PEACHはその名の通り、PCI Expressでノード間を接続してしまうという筑波大考案の仕掛けである。もちろん、PCI Expressで接続できるのは数m程度の長さが限界で、Gbit EthernetやInfiniBandのような長い接続はできないが、小規模なクラスタなら十分である。

通常のPCI ExpressはCPU側のRoot Complex(RC)とI/O側にあるEnd Point(EP)の間で通信を行うもので、計算ノード間を接続することはできないが、筑波大のPEACHではPCI Expressはパケットの伝送路として使用し、PEACHチップにルータ機能を持たせることにより、小規模な高速ネットワークが作れるようになっている。

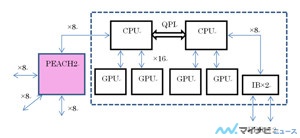

HA-PACSのTCA部では、このPEACHを改良したPEACH2を使用する計画である。PEACHはカスタムASICであるが、PEACH2はAlteraのFPGAで実現する予定である。そして、PEACHでは各ポートはPCI Express2.0の×4レーンであったが、これをPEACH2では×8に倍増する。また、PEACHではマイクロコントローラで処理していた機能をPEACH2ではハードワイヤ化して性能を改善している。

PEACH2は、×8を4ポート持ち、それらのポートの間でPCI Expressのパケットをルーティングする機能を持っている。

写真はボードのプリント板で、部品が未搭載のものである。写真の右側のドータボードの左に見える金色の部分にFPGAが搭載されることになる。なお、中央の空き領域にはLCDが搭載され、左側のチップコンデンサなどが搭載されている部分は、各種の電圧を作り出す電源部である。

TCA部の構成は、まだ、検討中で、決定したものではないが、一つの案では、ベースクラスタとほぼ同じSandy Bridge 2ソケットに4基のGPUを接続する構成のノードにPEACH2を接続する。

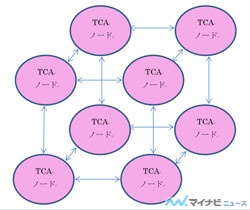

そうすると、このノードは3本のPCI Expressの手を持つことになる。この3本の手で4つのノードを完全結合することができるし、キューブ状に接続すれば8個のノードを接続することができる。更に、より疎な接続とすれば、さらに多くのノードを接続することができる。例えばキューブ状の8ノード接続の場合は、32基のGPUがPCI Expressで接続され、同一メモリ空間に存在することになる。

GPUのGDDRメモリは高速であるが、そのためGPUと1対1接続となり、メモリ容量はM2090の場合で6GBとCPUに比べて小さなメモリしか持てない。このため、多くのメモリを必要とするアプリケーションではGPU間で独立したメモリ空間への明示的なデータ転送が必要となり、計算効率が低下してしまう。これに対して、PEACH2で、例えば32GPUを共通メモリ空間に配置すれば、32倍のメモリを必要とする問題をこれらのGPUグループで処理することができるようになり、GPUクラスタの適用範囲が大きく拡張できる。この場合もGPUのメモリ間でのデータ転送は必要になるが、CPUの介在なしにPEACH2チップとPCI Express2.0のリンクを経由するだけであり、オーバヘッドが少ない転送ができる。

なお、同一ノード内の4基のGPU間の直接データ転送は現在でも可能であり、これと比較するとPEACH2を使うことによるアドレス空間の拡大は、キューブ状の接続の場合、8倍である。

TCA部は、このTCAノードを64ノード持つ予定である。CPUはベースクラスタ部と同じであるが、GPUの方は、3月22日にNVIDIAが発表したKepler GPUを使用する予定である。3月22日の発表はPCグラフィックス用KeplerでありHPCに使用するTesla系のKepler GPUは未発表なので、正確な性能値は不明である。しかし、PCグラフィックス系Keplerでは前世代の製品と比較して性能が2倍になっており、Tesla系も現在のFermiベースのM2090の2倍と考えると、1.3TFlops程度の値になると考えられる。この値が正しいとすると、CPUのFlopsを含めると、TCAノードのピーク演算性能は5.5TFlopsに達する。これが64ノードであるので、TCA部全体では352TFlopsとなり、ベースクラスタ部の802TFlopsと合わせると1.154PFlopsのシステムとなる。

ベースクラスタ部のIBスイッチのポート数に余裕を持たせてTCAノードも同じスイッチに繋ぎ込むことも考えたが、コスト的に高くなるので断念し、TCA部には64ノードを接続する独立したIBスイッチを置き、ベースクラスタ部のIBスイッチとの間は8ポート×2の接続という疎な接続形態とする。構造も違うので、ベースクラスタ部とTCA部で密に連携した処理を行うことは少ないと考えられ、この程度の接続で良いと考えているという。

TCA部は、2012年度末には完成の予定であり、HA-PACSは2013年には1PFlops超えのシステムとなる予定である。

そして、HA-PACSは戦略分野5の「物質と宇宙の起源と構造」の研究推進に貢献するとともに、アプリケーション、アルゴリズム、アーキテクチャの研究者の一体となった体制で研究を進めることにより、ExaFlops時代のスパコンアーキテクチャや使い方の知識の獲得に大きな貢献をすることが期待される。