Lattice Semiconductorは、同社のFPGA「LatticeECP3」ファミリに通信、マルチメディア、サーバ、モバイル各プラットフォーム向けに2.5GbpsのPCI Express(PCIe)2.0仕様に対応した製品を発表した。

同FPGAとPCIeのIPコアは、PCI-SIGワークショップで行われたPCI-SIG PCIe v2.0規格適合性テスト、および1レーンまたは4レーン構成の相互接続テストに合格しており、既存のPCIe 2.0対応システムと相互接続性のあることが実証されている。

PCIe v2.0仕様は2.5Gbpsでの動作が可能だが、PCIe v1.1と異なり、ループ帯域幅の特性はより厳密なものとなっており、同ソリューションは、5Gbpsで動作するPCIeリンクは不要ながら、PCIe v2.0互換を必要とする分野のカスタマに、PCIe v2.0準拠システムながら低コストなFPGAを提供するものと同社では説明している。

また、Trellisysとの協業により、同社PCIeの×1および×4のIPコア向けに、堅牢性の高いPCIeバスファンクショナルモデル(BFM)も提供される。同PCIe BFMは、ユーザ/アプリケーションロジックの一般的な実装部であるトランザクション層に焦点を当てたものとなっている。

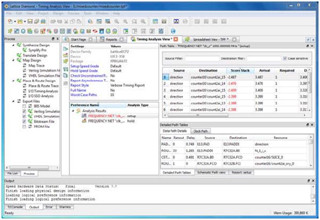

同社PCIe BFMはVerilogおよびVHDLに対応しており、Aldec Active-HDLおよびRiviera-PROの両シミュレータで検証されている。これはコンパイル済みコードとして提供されるが、先進的な検証スイートの基盤となるプロシージャライブラリがユーザに提供されており、設計者はLattice Diamond 1.2以降の設計ツールスイートに含まれるIPexpressツールを用いて、LatticeECP3のPCIe 2.0準拠システムの評価および設計を行うことができるようになっている。

なお、Lattice PCI Express IPスイートは現在、単独の販売促進プロモーションの一環として、99ドルで提供されている。また、限定プロモーション後の通常価格は995ドルを予定しているという。