毎度、ベタ遅れのIDFのお留守番レポートである。今年も4/12・13日に北京でIDF Beijing 2011が開催された訳だが、今回のIDFは目玉が無いというか、しいて言えばAtom Z670シリーズといった程度。Hisa Ando氏のレポート位しか面白い話はなかったわけで、実際テクニカルセッションの内容も、既に公開された内容ばかりといった具合。個人的にはThunderboltでもう少し細かい話があるかと思ったが、蓋を開けてみると新しい話は皆無。肩透かしを食らった感じだ。そんなわけで、IntelではなくGOLD SponserだったHynix Semiconductorのセッションから1本と、これに加えてちょっと次々世代プロセスの話をご紹介したいと思う。

Hynix Session

Hynixのセッションは、当然ながら自社製品のソリューションを説明するものであるが、まずはマーケット概観である。

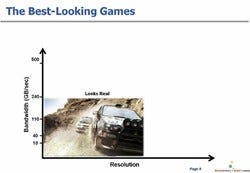

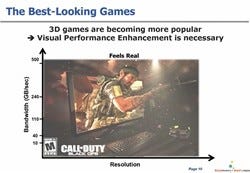

まずGPUに関して言えば、特にゲームが一貫してより高いバンド幅を必要とし続けている(Photo01~04)。

|

|

|

Photo01:Virtua Fighterあたりだろうか? ただNV1だともっと帯域は少なかった気がするのだが。 |

Photo02:CRYSiS。"Satisfying"するかどうかは、当然人による気が。 |

|

|

|

Photo03:DiRT 2。たしかにだいぶ描画は改善されたが、Realにはまだちょっと遠い気が。 |

Photo04:多分3Dという意味であろう。500GB/sec位ではまだ実際に人が画面から飛び出せたりはしない。 |

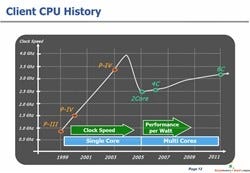

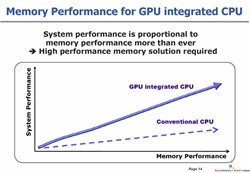

一方汎用CPUは、マルチコア化によって一旦は動作周波数が下がったものの、マルチコア化が進み、しかも動作周波数も次第に戻しつつある(Photo05)。加えて、Integrate GPUの方向性をIntel/AMD共に明確に打ち出しているから、CPU自身が要求するメモリ帯域は更に大きくなるわけだ(Photo06)。

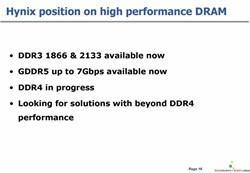

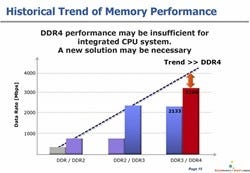

問題は、こうしたトレンドに対応するメモリが間に合わない事である(Photo07)。以前こちらでMemcon 10におけるJEDECのProjectionをご紹介したが、DDR4世代は最大4.3Gbps(4266Mbps)を想定している。ただこれは落とし穴があり、チップそのものは4.3Gbpsが可能と見られつつも、配線が現在想定しているSingle Ended Signalingで可能となるかどうか、まだ未知数な事だ。以前のJEDECロードマップでは、DDR4世代はSingle EndedとDifferentialの2種類の配線方法をサポートし、Single Endedでは3.2Gbps、Differentialで6.4Gbpsを狙うというアプローチだった。今回のHynixのレポートは、おそらくこのSingle Endedは3.2Gbpsという数字をそのまま使ったものと思われる。

|

|

Photo07:逆に言えば、DDR4で本当に4.3GHzが可能になれば、このグラフにおけるDDR4のMissmatchは解消される訳であるが、さてどうなるか。ちなみにJEDECの現在の予想では、2015年以降になるとされている。 |

さて、ここからがHynixのSolutionである。まず現状はこんな感じ(Photo08)。

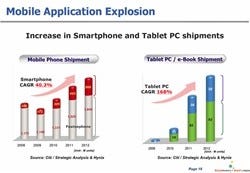

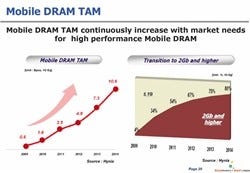

DDR3-1866/2133はHynix以外にもサンプル出荷とか量産を始めているベンダもあるので、そう不思議ではない。で、詳細であるがここで多くの時間を費やしたのがMobile向けソリューションであったのがちょっと面白い。携帯電話の場合、FeaturePhoneではそれほど大容量メモリが要求されないが、SmartPhoneではいくらメモリがあっても足りない、というのが利用者側の実感であろう。更にTabletやe-booksも、これまた急速に伸びつつある(Photo09)。この結果として、Mobile DRAMの出荷量が増え、またMobile RAMに要求される容量も増える傾向にあるとされる(Photo10)。

|

|

|

Photo09:右グラフは肝心の項目が書いてないが、おそらく青がTablet、緑がe-booksであろう。 |

Photo10:コモディティ製品は売り上げが立っても利益率が低いため、(利益率を相対的に高く取れる)モバイル向け製品を充実させる事は、例えばエルピーダなども以前から公言している話であり、Hynixも例外ではない、ということだ。 |

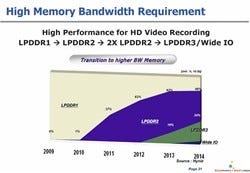

さて、面白いのはここからである。こうしたトレンドに伴い、より高い帯域が必要とされるのは当然で、この結果、今年はLPDDR2がかなりの割合を占め、2012年からはLPDDR3も立ち上がるとしているが、面白いのは2013年あたりから立ち上がるとされるWide I/Oである。Wide I/Oは構造上、TSVを使ってメモリチップとSoCを3次元で接続する事を念頭においているが、Hynixはこれについて2013年から提供を予定していることを明らかにした(Photo12)。

|

|

|

Photo11:Wide I/Oはまだ標準化の途中だったと記憶しているが、現時点では512bit幅以上のMemory I/Fをさす(1024bit幅の計画をしているベンダもある)。Cadenceは今年3月、業界初となるWide I/OのIPを発表している。 |

Photo12:Mobile向けの場合、チップの発熱によるメモリの動作への影響が少ないと見られるためか、最初にここでTSVが実用化されると見られている。とはいえ、このロードマップではあと2年で提供が開始されることになっているが、さて。 |

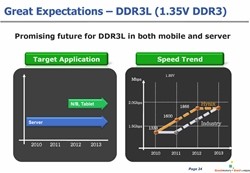

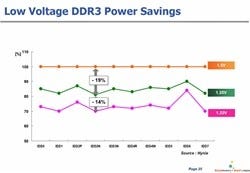

ついでコモディティ向けである。既に一部のサーバ向けなどには1.35V動作のDDR3Lの提供が開始されているが、来年からはノートPCやTabletなどもDDR3Lに移行を開始するだろう、というのがHynixの予想である(Photo13)。ちなみにDDR3Lの主要な特徴は省電力性であり、1.35Vでは平均19%、1.25Vでは更に平均14%の消費電力削減が可能としている(Photo14)。

|

|

|

Photo13:このデマンドにあわせて、Hynixは業界トレンドを1年前倒しして提供するとしているが、これも蓋を開けてみると、主要メーカーが全部前倒しになりそうな気がしなくもない。 |

Photo14:横軸はDDR3の動作モード。とはいえ、1.35Vはともかく1.25Vまで電圧を下げるには、現在の30nm台のプロセスをもう1~2段微細化を進めないと難しそうな雰囲気ではある。 |

Hynixのセッションでは他にもDDR4の紹介とかServer Marketの話も行われたが、こちらはあまり目新しい話は無かったので今回は割愛する。一番興味深いのはTSVで、これはHynixのみならずSamsung Electronicsやエルピーダメモリなど、主要なメーカーは皆チャレンジしている話である。TSVに関してはSEMATECHの取り組みが(単にTSVの技術だけでなく、EDAツールなどの対応なども含む広範な範囲をカバーしているという点で)かなり先行しているが、今年3月にHynixもこのSEMATECHの3D Interconnect Programに参加しており、逆にここから2013年には業界全体がTSVに向けて本格的に立ち上げを開始すると予想できるわけで、ちょっと楽しみである。