本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

この追体験設計では4004の主要コンポーネントの設計を行ったが、IO命令をデコードして制御信号を生成する回路と、RAM、ROMの選択信号を生成するCM Logicについては設計を行っていない。これらはいずれも比較的簡単な回路であるので、興味のある読者は応用問題としてどのような回路になるかを考えて戴きたい。

もう一つ、設計に組み入れられていないのはReset信号の扱いである。Reset信号についてはタイミング発生回路のところで、リセット解除後にA1サイクルから始まる設計と述べたが、それ以外に、最低限、PCレジスタの値を既定値(例えば0番地)として、最初に実行する命令をROMから読み込めるようにする必要がある。また、4004では、それ以外のレジスタについてもリセットによりゼロクリアされるレジスタがあるのかも知れないが、データシートでは触れられていない。ということで、この追体験設計では、PCを含めてレジスタをリセットする機能は実装されていないが、この機能は、非同期リセット端子をもつFFを使いリセット信号を接続すれば容易に実現できる。

この追体験設計では、バスの制御信号の生成回路などは一部の例だけしか論理設計を行っていないので、概算であるが、回路量は以下のようになっている。

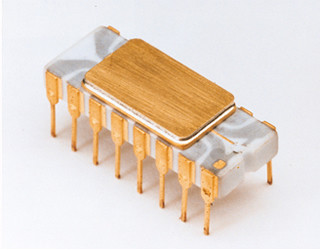

全体で約8600トランジスタと、オリジナルの4004の約4倍の物量となったが、主因は4004のようなP-MOS 2相式ダイナミック回路ではなく、CMOSを用いたことである。4004と同じ回路形式を用いた場合、寄生容量に溜まった電荷で情報を保持するダイナミックのラッチ回路は3トランジスタで作ることが出来る。また、FFも8~9トランジスタ程度で作ることができるので、ラッチとFFで3500トランジスタ程度減少する。また、ゲートやマルチプレクサのトランジスタ数も半分程度に減少すするので、この部分で1900トランジスタ程度減少し、4004と同じP-MOSダイナミック回路を使用することにより合計3200トランジスタ程度に減少する。

まだ、4004の2300トランジスタと比べると900トランジスタ程度多いが、この追体験設計では、分かりやすさを優先して、ある程度冗長な設計となっている部分もあるので、ゴリゴリとトラジスタ数を減らすような最適化をしていけば、かなり近いところまで行けるのではないかと思われる。

補足であるが、ダイナミック回路を使うとラッチやFFのトランジスタ数を大幅に節約できるが、寄生容量に溜まった電荷で情報を保持するので、時間が経つと漏れ電流により、記憶した状態が消えてしまう。従って、クロック周波数に下限があり、また、問題が発生した場合にクロックを止めて原因を調査するというようなことが出来ないという欠点がある。

長々とお付き合いを戴いたが、以上でIntel 4004の論理設計の追体験は終わりである。4004という一番簡単なマイクロプロセサであるが、プロセサというものがどのように作られているかという感じは掴んで頂けたのではないかと思う。

なお、Faggin氏が4004を設計した時代には、人手でこれらのデコーダや制御信号発生回路をゲートやトランジスタを使って設計していたが、昨今では、論理回路の自動合成システムが広く使われており、制御表相当の情報を入力すれば回路を作ってくれる。ということで不規則な制御信号の発生回路を作る手間は大幅に削減されている。

我々の追体験設計はこれで終わりであるが、Faggin氏の設計はこれでは終わらず、更に、トランジスタを並べ、その間を配線で接続し、物理的に回路を作る必要がある。そして、この図面を大きな方眼紙に書き、色鉛筆で、トランジスタの拡散層、ゲートとなるポリシリコン層、アルミニウムの配線層、アルミニウム配線と拡散やポリシリコンとを接続する孔を作るコンタクト層などに分解して塗り分ける。

それから、色鉛筆で色分けをした図を基に、各層別にルビリス(Rubylith)と呼ぶ赤いプラスティックフィルムが貼られた紙を使って、この赤いフィルムを鋭利なカッターナイフで切ってフィルムを剥がして白い紙の下地を出してコントラストの良い原版を作り、それを写真で縮小してマスクを作る。

10μm幅の配線を1cmにして1000倍で描いたとすると、この色鉛筆の図面やルビリスは4m x 3m程度の大きさであり、大変な作業である。論理設計から始まって、これら全てを1年足らずで成し遂げたのは驚異的であり、Faggin氏の猛烈な仕事振りが偲ばれる。

幸いなことに、今日ではこれらの配置配線作業の大部分はCADが自動でやってくれる。また、各層に分解してマスクデータを作り、各マスクの図形の位置関係が正しいか、設計ルールに違反するような寸法のところは無いかなどのチェックもCADがやってくれるので、論理設計以降の手間は4004の時代に比べると大幅に省力化されている。また、このような自動化が無ければ、昨今の10億トランジスタを超えるようなプロセサの開発は不可能である。