本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

「4004の設計を追体験する」のシリーズで、連載の第49回に4004のKBP命令のエンコーディングについて書いたが、4004のマニュアルをお持ちの読者の方から実物と違っているとご教示を戴いた。

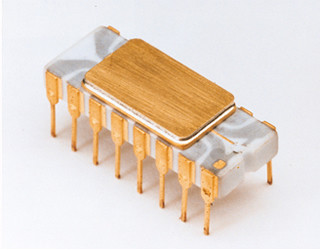

この4004の設計の追体験シリーズは、商用として販売されたものとしては、多分、一番簡単なプロセサである4004を題材としてコンピュータの設計を学ぶというのが目的であり、設計されたプロセサの仕様が4004と完全に一致することは必須ではないのであるが、折角、教えていただいたので、4004と同じエンコードを行うユニットを設計してみようというのがこの補遺である。

第49回では、ACCレジスタに読み込まれたキーの情報を2進数に変換してBit-2、1で示し、どれかのキーが押されたと言う情報をBit-0として出力すると言う仕様を採用し、これを実現する回路を設計した。そして、別解のようにキーの押下信号のACC0~3を1~4に対応する案も有りうると書いた。

読者の方から教えていただいた4004の実装は、別解の方で、更に、2つ以上のキーが押されていると全ビットが"1"になるのだそうである。確かに2つ以上のキーが押されている状態はエラーであり、それを検出することは必要であるので、どのキーも押されていない状態、4つのキーのどれか一つのキーが押されている状態、2個以上のキーが押されている状態を識別するのは意味のある区別である。

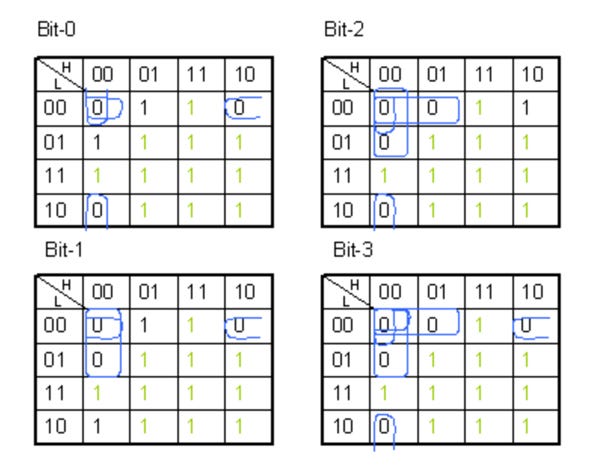

この4004で実装されたエンコードのカルノーマップを次の図に示す。

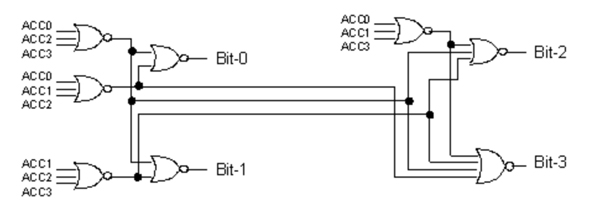

この図で、赤い字になっている部分は、1つ以上のキーが押されているケースで、Bit-0~3出力の全てで"1"になっている。一方、黒字の"1"、"0"は押されたキーをエンコードしている。このカルノーマップでは"0"の数が少ないので、OR-AND回路で"0"のエントリを纏める回路を設計する方が簡単である。このカルノーマップで青線で書かれたボックスはOR-ANDでこられの条件を実現する場合の各項を示している。例えば、Bit-0では、Hが*0(ここで*は"0"でも"1"でも良い)、Lが00のケースは出力は"0"であり、また、ACC2以外が全て"0"の場合も出力は"0"である。従って、Bit0=(ACC2+ACC1+ACC0)・(ACC3+ACC1+ACC0)で生成することが出来る。同様に、Bit-1~3に対して青線のボックスを纏めて論理回路としたのが次の図である。

4004と一致するキーボードエンコード回路の設計は、以上で終わりであるが、ついでであるので、第49回設計の考え方で2つ以上のキーが押された状態を識別する案を考えて見よう。

第49回設計では、Bit-0がキーが押された状態を示し、Bit-2とBit-1で押されたキー番号をバイナリで表示し、Bit-3は未使用という仕様であったが、ビット順を多少変更し、Bit-3 はキーが押されたことを示すビット、Bit-2 は複数キーが押された状態を示し、Bit-1 とbit-0で押されたキーを0~3で示すという仕様のエンコードを考える。

この仕様は、Bit-3を見てキーが押されていなければキーのスキャンを繰り返し、キーが押されていれば、Bit-2 を見て、単一キーが押されている状態であることを確認してから、Bit-1、bit-0を見て押されたキー番号を取り出すという使い方を想定している。

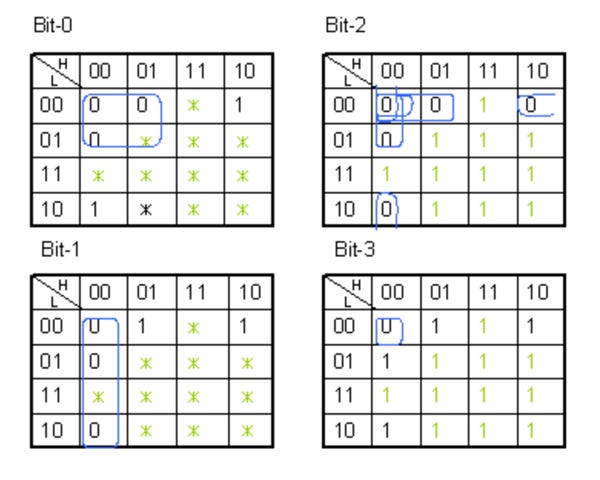

このエンコードのカルノーマップを下図に示す。

このエンコードのミソは、複数キーが押された場合の出力を11**として下2ビットの値を任意(Don't Care)とした点である。このため、Bit-0とBit-1は上図の青線のブロックのように纏めることが出来る。しかし、Bit-2のマップには、このような任意の出力が無いので、4個の青線のブロックが必要となる。そして、Bit-3のマップも任意の出力はないが、この出力が"0"となるのは、ACC3~0の全部が"0"となった場合だけである。

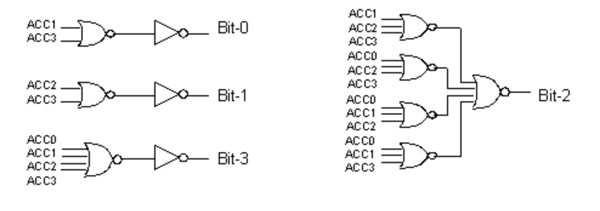

これを論理図として書いたものが次の図である。Bit-0、1、3の回路はビット順は変わっているが、基本的に第49回の回路と同じである。一方、複数キーが押されたことを検出するBit-2は4004のエンコーダ回路のBit-3と同じであり、合計5個のNOR回路が必要となる。

なお、49回のエンコード回路で、キーが押された状態を示すBit-0を作る回路が4入力NANDとインバータで構成されているが、これは誤りであり、次の図のBit-3のように、4入力NORとインバータするのが正しい。謹んで訂正させて戴きたい。