本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

命令レジスタとデコーダ

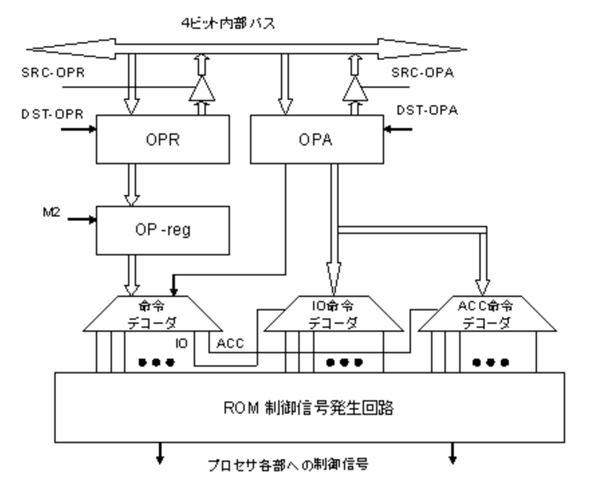

命令レジスタと命令デコーダはROMから読み出された命令を受け取り、命令を解釈してプロセサ全体の制御を行う、いわば、プロセサの頭脳部分である。

この図では、4ビットのレジスタやトライステートバッファは纏めて1個のシンボルで表記し、太い矢印で4ビットを纏めた信号を表している。OPRレジスタはROMから読み出された命令をM1サイクルに受け取って格納する。

16ビット命令の場合は、命令の2バイト目を処理するときにOPRレジスタの内容が変わってしまうが、命令の種別がわからなくなってしまっては困るので、それをM2サイクルにOP-regにコピーしておく。

OPAレジスタはROMからの命令の後半をM2サイクルに受け取って格納する。OPAレジスタも命令の2バイト目を処理する時に変わってしまうが、OPAの内容は最初の8サイクルに使われてしまい、2バイト命令の後半では必要なくなるので、こちらはコピーを作らなくても問題は生じない。

この図に描いた命令デコーダはどのレジスタからデコードすべき信号が供給されるかを示したものであり、詳細な機能は省略しているが、命令デコーダはバス制御信号の発生のところで書いたデコーダであり、ACC命令のデコーダはALU制御信号のところで触れたものである。これらのデコーダは4ビット入力を全てデコードする必要は無く、必要な制御信号を作るのに必要の無い出力は省略してゲートを節約すれば良い。