AMD GPU(Photo02)

-

Photo02: 保護から約1カ月後。もう里親さんも決まり、里子に出る直前の写真。ベッドは潰して使うのがジャスティス。ちなみに4匹まとめての里子入りが決定。この写真には茶トラが写ってないが、どっかそこらに落ちてたと記憶している

絶対性能はともかく、市場シェアという意味ではまだまだNVIDIAに水を開けられているAMD。2022年はまずRadeon RX 6500と6400からスタートするようだ。元々Navi 2シリーズは既に発表済のNavi 21(Radeon RX 6800/6800 XT/6900)、Navi 22(Radeon RX 6700 XT)、Navi 23(Radeon RX 6600/6600 XT)に続き、よりDie sizeの小さなNavi 24が噂されていた。これがRadeon RX 6500 XT、及びRadeon RX 6400としてCESで発表。今年第1四半期中に発売開始されるのではないか、と見られている。

Navi 24は最大構成で16CUと、Navi 23のほぼ半分になる。Infinity Cache容量は16MBと目されている。ちなみにRadeon RX 6400の方はOEM専用となり、リテールマーケットに流れてくるのはRadeon RX 6500 XTのみとなりそうだ。こちらは16CU/1024SPで動作周波数は2.2GHz(Base)~2.5GHz(Boost)程度。メモリはGDDR6 16Gbps/128bitで容量は4GBとみられる。TBP(Total Board Power)は100Wほどで、残念ながら補助電源レスは難しいようだ(OEM向けのRadeon RX 6400は12CU/768SPで動作周波数も最大2GHzほど、メモリもGDDR6 14Gbps/128bitで4GBとなる。その代わり、こちらはTBPが75W枠に収まり補助電源レスが実現できるようだ)。

特徴的なのは、このNavi 24はTSMC N6で製造される事である。先にCPUの所でAMDのZen 4 IODには1~2CUのNavi 2が搭載されると説明したが、これと共通のIPということになる訳だ。要するにZen 4 IODに先立ってNavi 24で確認しておくという話であるが、別にその検証だけが目的でN6を使ったという訳でもなさそうだ。要するにローエンドだからコストを抑えたいという目的ではマスクの数が(ArF+液浸→EUVの移行で)減らせることで初期コストが減らせるし、N5は既にZen 4や次のNavi 3で一杯になっているから、余っているのはN6しかないという辺りだろう。勿論N6の習熟という意味でも意味はあるとは思うのだが。

さて、Radeon RX 6500 XTはもう明確にエントリー向けである。Radeon RX 6600がFull HD Gaming向けだった訳だが、これよりも更に性能が低く、しかもメモリが4GBなので、Full HDでも描画オプション最大とするのはまず無理である。まぁCasual Gaming向けといったあたりだろうか。ただ昨今はそのCasual Gaming向けの製品も市場に払底しているので、こうしたマーケットに適切な価格できちんと製品供給できれば、シェア拡大に役に立ちそうではあるのだが。

次がRNDA3ベースのNavi 30シリーズの話であるが、今聞こえている話で言えば

- RDNA3世代ではCU(Compute Unit)が無くなり、代わりにWGP(WorkGroup Processor)がベースになる。WGPはRDNAの世代で導入されたもので、RDNAの実装では2つのCU+共有キャッシュが1つのWGPとして管理されていた。RDNA3世代でもこれは同じだが、もうCUという概念が無くなった。言い換えると、従来のCU(64SP)構成から今度は128SPが最小単位になった格好だ。もっともRDNA2では、2つのCUで命令キャッシュとかを共有するというむしろ複雑な構成になっていたから、これはむしろ内部構造がすっきりしたと言えるかもしれない。もっと今度は、そのWGPを5つまとめたShader Arrayという名称のグループが最小単位になるようで、単に64SP単位から128SP単位に変わったという話なのかもしれない(RDNAでも、5つのWGPで一つのL1 Cacheを共有する形になっていたが、Shader Arrayという名称は無かったと記憶している)。

- マルチチップ構成が前提になるらしい。ハイエンドのNavi 31とミッドレンジのNavi 32はは、3チップ構成である。要するにGPUのDie(GCDと呼ばれるらしい)×2+Infinity CacheのDie、という格好である。マルチチップのDie、といっても昔のCrossFireと異なり、2つのDieは協調して動くことになる。簡単にまとめたのが図1である。各々のGCDはShader Array×4~6、つまりWGPを20~30個、SPで言えば2560個~3840個内蔵する格好である。2つのコアでトータル5120~7680SPとなり、Radeon RX 6900 XTの5120SPを上回る事になる。Infinity Cacheは、ハイエンドで512MB、ミドルレンジで256MBとなっており、ひょっとするとハイエンド品はミドルレンジの256MBのDieの上に、3D V-Cache方式でもう256MBを乗っけている可能性がある。なおGCDがTSMC N5、Infinity CacheはTSMC N6らしい。

- メモリバスはハイエンドでも256bitと伝えられている。まぁInfinity Cacheがあれば、必ずしもメモリバスを広げる必要性は無いのかもしれない。メモリコントローラ、それとPCIeのコントローラはInfinity CacheのDie側に集積されるとみられる。

といった感じだろうか。ちなみにGCDとInfinity Cacheの接続は、Radeon Instinct MI200シリーズで採用されたEFB(Elevated Fanout Bridge) 2.5Dが利用されると思われる。

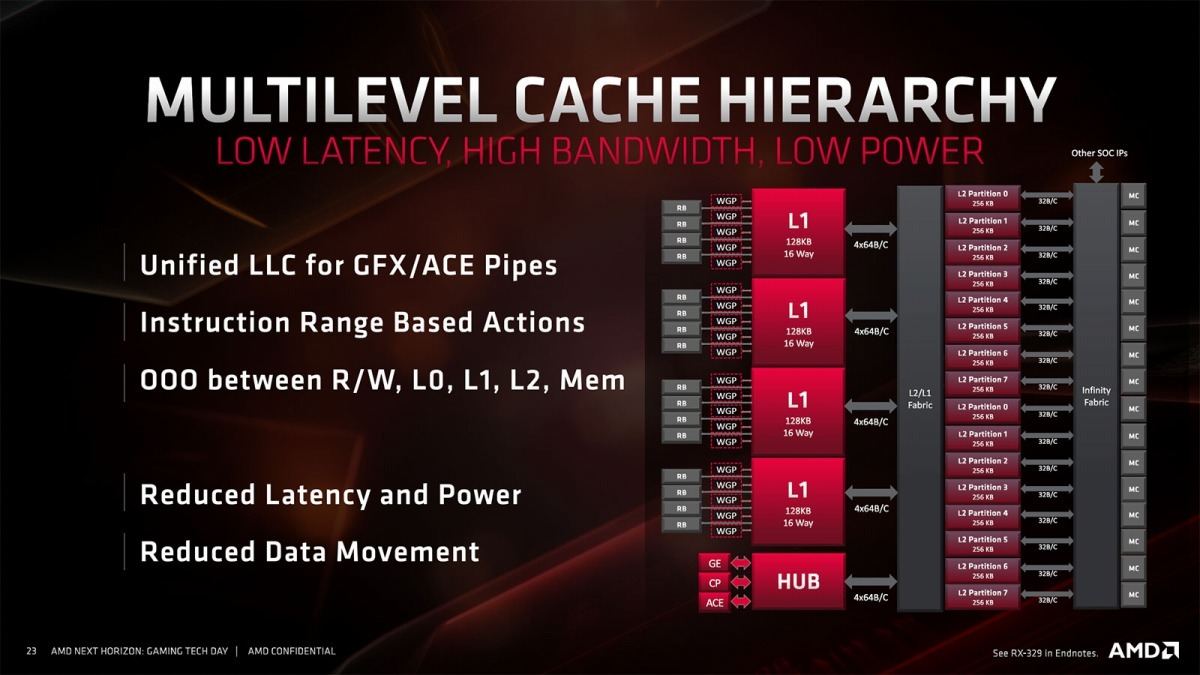

ここで気になるのは、「マルチチップ構成でRender Backendの性能が出るのか?」という話であろうかと思う。もともとRDNAの世代でも、Deferred Rendering(遅延レンダリング)を多用する場合の性能を改善するために、RB(Render Backend)とWGPの間にL1 Cacheを挟んでいる(Photo03)。今回の例でいうなら、同じShader Arrayに属する5つのWGPの間は、L1を利用してDefferd Renderingが行えるが、これ以外についてはどっちみちL2ないしInfinityFabric経由となる訳だ。なので、ちょっとPhoto03の右下を描き換えて拡張したのがPhoto04だが、こんな感じになれば異なるDieの間であってもGCD #1 L1→GCD #1 L2→InfinityCache→GCD #2 L2→GCD #2 L1という最速のパスでアクセスできることになり、それほど深刻な性能低下は発生しないのではないか、と考えられる(さすがにMonolithic Dieよりは遅いのは間違いないとは思うが)。

-

Photo03: 昔このスライドをどこかの記事で掲載した記憶があるのだが、ぱっと見つからなかったので再掲。2019年6月に開催された"Next Horizon Gaming 2019"というイベントでのものである。

-

Photo04: これはPhoto03の図をPhotoshopでつぎはぎしただけである。この例でいうなら、L2 PartitionとInfinity Fabricを繋ぐ部分で物理的にダイが分かれ、間をEFB 2.5Dで繋いでいると思われる。

ちなみにNavi 31が60WGP(7840SP)+512MB Infinity Cache、Navi 32が40WGP(5120SP)+256MB Infinity Cacheという話になっており、続くNavi 33はMonolithic Die構成になるようだ。ちなみにNavi 31とNavi 32で物理的にDieが一緒なのか異なるのか、は不明である。案外Dieそのものは共通かもしれない。個人的には6WGPと4WGP、というのはちょっと収まりが悪い感じである。これが8WGPと4WGPとか6WGPと3WGP、とでもいうのなら別々のDieなんじゃないだろうか、と思うのだが。

さてこのRDNA、最初に出てくるのはNavi 31ベースで、Radeon RX 7000シリーズになるのだろうか? こちらは2021年10月にTape outしたという情報がある。だとすれば、最初のプロトタイプが出てくるのは今年の3月とかそのあたりで、COMPUTEXのタイミングで試作機の動作デモとかが見られるかもしれない。量産そのものは2022年の第3四半期以降という話である。AMDの厄介なのは、Zen 4とTSMC N5の取り合いになっている(おまけにIntelやNVIDIAとも取り合いになる)事で、実際の出荷開始はN5プロセスをどれだけNavi 31に割り当てできるかで決まる事になりそうな感じである。

続くNavi 32は、恐らくは2023年以降に投入となりそうだ。