龍谷大学、奈良先端科学技術大学院大学(NAIST)、北陸先端科学技術大学院大学(JAIST)の3者は9月3日、印加電圧の履歴によりキャパシタンスが変化する回路素子である「メムキャパシタ」と自律局所学習を用いて、脳の構造を模倣したニューラルネットワークシステムである「ニューロモーフィックシステム」を開発したことを発表した。

同成果は、龍谷大 先端理工学部 電子情報通信課程の石崎勇真大学生、同・木村睦教授(NAIST 先端科学技術研究科 客員教授兼任)、同・宮部雄太氏、同 吉田誉氏、同・小川功人氏、同・横山朋陽氏、JAIST 先端科学技術研究科の徳光永輔 教授、JAISTの羽賀健一氏(研究当時)、NAIST 先端科学技術研究科の中島康彦 教授らの共同研究チームによるもの。詳細は、ニューラルネットワークと学習システムを扱う学術誌「IEEE Transactions on Neural Networks and Learning Systems」に掲載された。

生物の脳の構造を模倣し、ニューロン素子やシナプス素子を実装する「ニューロモーフィックシステム」の人工知能(AI)への活用が期待されているが、現状、AIとしての最適化は不十分とされている。その原因は、主に、「大規模な模倣回路やメモリスタ(可変抵抗素子)を使うため、DC電流や過渡電流が大きく、電力消費量が多大」、「大規模なシナプス素子の結合強度の制御回路を使うため、サイズが大きい」という2つの課題があるため、とされている。

そこで研究チームは今回、ニューロモーフィックシステムの開発において、電力消費量の低減に向け、DC電流がなく、過渡電流も減らせる「メムキャパシタ」を採用する一方で、「自律局所学習」を用いることで、回路のダウンサイジングを図ることにしたという。

今回の研究では、強誘電体キャパシタを用いたメムキャパシタを選択。将来の高集積化が容易となるよう単純な構造が採用された。具体的には、ビスマス(Bi)、ランタン(La)、チタン(Ti)からなる合金の酸化物「Bi3.25La0.75Ti3O12」(BLT)の薄膜の液相プロセスが用いられ、クロスバー型のメムキャパシタを作製。印加電圧の履歴により強誘電体キャパシタの自発分極が変化することで、キャパシタンスが変化する回路素子が実現されたとする。

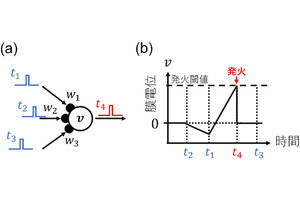

一方の自律局所学習は、単一素子が自分自身の駆動条件のみで特性を変化させる学習方式であり、メムキャパシタの電圧履歴のキャパシタンス特性を上手く利用することにより、シナプス素子の結合強度の制御回路などなしに、メムキャパシタだけで、ニューロモーフィックシステムに学習させることを可能とした。

学習フェーズでは、シンプルに、クロスバー型の横方向に配された電極と、それに直行する縦方向の電極に電圧を印加するだけで、必要なキャパシタンスの変化が誘起される仕組み。推論フェーズも、横電極に電圧印加し、縦電極の電圧を読み取るだけのシンプルな仕組みを採用。

実験では、このニューロモーフィックシステムを用いて、アルファベットの「T」と「L」の記憶が行われ、わずかに異なるパターンが入力されるとき、記憶した「T」または「L」のより近い方が出力されることが確認されたという。

この動作は「連想記憶」というもので、文字認識や画像認識に直接に応用できるものであると同時に、問題設定により、さまざまな人工知能の取り扱う課題に応用できるものだという。また、そのサイズも、従来の人工知能では、たとえばコグニティブ・コンピューティング・システムのサイズは冷蔵庫10台ほど、電力消費は数百kWといわれているが、今回の研究の基本的な成果をもとに、同様の機能のシステムを構築する場合、1チップLSI程度のサイズで20W程度の消費電力で実現できることが期待されるとしている。