韓国の半導体組み立て・テスト専門会社であるSNPTは、同社独自のサイズの異なるMLPGAパッケージを用いることで、さまざまな規格とサイズの半導体チップを一度にパッケージングする技術「Multi-array structure semiconductor substrate」を実用化したと韓国メディアEtnewsの英語版(Korea IT News)が報じている。

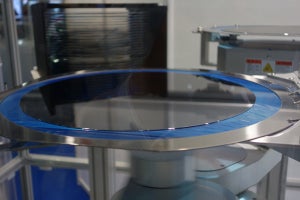

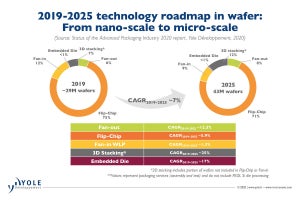

半導体のパッケージング工程は、半導体のダイを保護したり、プリント基板と接続しやすくするために行われるもので、パッケージ基板の大手企業としては、イビデンや新光電気などがあげられる。近年は、ウェハレベルパッケージング(WLP)などの高度な技術も出現してきたが、それでもパッケージング市場の8割はまだ基板を用いたパッケージングが主流であるという。

今回実用化された一括パッケージング技術は、従来の1枚の基板に1つのダイをパッケージ化するという既存方法の制限を取り払うことを可能とするもので、これにより研究開発用の少量生産半導体チップの実装に要する期間の短縮を図ることができるようになるという。

すでに6月に特許登録を実施し、韓国内の半導体メーカーと6つの国内ファブレス企業への半導体パッケージングプロセスに適用したという。SNPTは、中小規模のファブレスや半導体を設計・開発する大学など、研究開発用半導体市場をターゲットにしており、米国と中国で海外特許を申請する準備を進めることで、これらの国々へも売り込むとしている。

同社によると、「半導体パッケージング基板は海外への依存度が高いため、ほとんどの基板を輸入して使用する必要がある。SNPTによって開発された方法は、1つの基板で10を超える規格やサイズの異なる半導体パッケージングに対応できるので、基板の節約になる。複数の種類の半導体を同時に製造できるため、複数のプロセスで製造されるファブレスチップの開発期間を短縮できるようになった」とのことで、最短で1〜2日で生産受託品を出荷できると説明している。

なお、韓国政府は2030年に「総合半導体強国」になるという宣言をしており、ファブレスや研究機関による新規半導体開発の支援・育成は、同分野の人材育成とともに最重点施策の1つと考えられ、SNPTにおけるファブレス・研究機関向けパッケージング技術開発もその一環とみられる。