Xilinxは米国時間の2月20日、同社のRF対応SoCであるZynq UltraScale+ RFSoCの最新動向に関してニュースリリースを出し、6GHz帯までの周波数に対応した製品展開を明らかにするとともに、2月25日からバロセロナで開催されるMWC 2019でデモを行うことを発表した。

この発表に併せて、Zynq UltraScale+ RFSoCに関する説明会を日本法人であるザイリンクスが開催したので、内容をご紹介したいと思う(Photo02)。

もともとXilinxは2017年10月に、Zynq Ultrascale+ RFSoCの第1世代製品を発表しており、2018年に出荷を開始している。

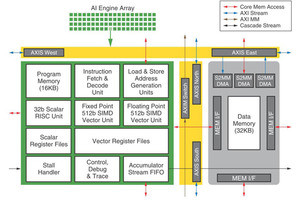

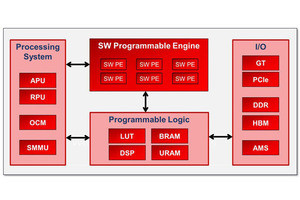

これは要するにZynq UltraScale+に4GspsのADCと6.4GspsのDAC、それとSD-FECを統合した(Photo03)ことで、様々なワイヤレスシステムのフロントエンドを1チップで実現できるというものである(Photo04)。

-

Photo03:Zynq UltraScale+ RFSoCの概要。Programmable LogicにADC/DAC/SD-FECを統合することで、別にRF Frontendを用意しなくてもそのまま無線を取り扱い可能となる

-

Photo04:RFSoCのターゲットは別に携帯電話だけでなく、電波が出るもの全般が対象となる

Photo05は実際にこのRFSoCを利用した例であるが、64×64のMassive MIMOを構成するにあたり、従来だとデジタルフロントエンド×4+アナログフロントエンド×32という構成が、RFSoCが4つに集積でき、消費電力と実装面積の大幅な節約が可能になった、としている。

-

Photo05:消費電力の節約に関して言えば、従来は4つのSoCと32個のアナログフロントエンドの間をJESD204のLinkでつなぐ必要があり、RFSoCにするとこの分が全部省ける事と、あとはデジタル側もRFSoCを使う事で省電力化が図れたことの両方の効果、という話であった

第2世代と第3世代を一気に発表

さて、ここからが本題である。現在出荷中(Gen1)のRFSoCの場合、4GHz帯までの周波数帯に対応できる。Photo06は横軸が周波数帯、縦軸が用途で、5Gであっても3~4GHz帯を利用できるほか、Lバンド/Sバンドのレーダー、それとDOCSIC 3.1/EDSにそのまま利用可能である。

これに続き今回、Gen2とGen3のRFSoCが発表されたが、これを利用するとまずGen2では4GHz~5GHz帯、5G NR(New Radio)のシステムが構築可能となる(Photo07)。

そしてGen3になると、5GHz~6GHzの、いわゆる5G NR-U(New Radio-Unlicensed spectrum)の帯域までカバーできるようになる事が示された。

まず5G NRに対応するGen2 RFSoCは来週のMWCでもデモが行われる予定で、すでに現在サンプル出荷中、量産出荷は2019年6月を予定している(Photo09)。

これに続くのがGen3(Photo10)で、こちらは2019年後半に量産出荷開始を予定している。

このGen2とGen3の特徴をまとめたのがPhoto11、Gen1~Gen3の仕様をまとめたのがPhoto12となるが、要するにGen2はMassive MIMOへの対応と5GHz帯への対応を追加したポイントリリーフ、Gen3が正統進化というかADCの14bit化とDACの10Gsps化を行った、Gen1の後継製品という扱いになる。

-

Photo11:実はGen1も含めて、Processing SystemやProgrammable Logicに違いは一切なく、相違点はDAC/ADC/SD-FECのみとなる(例外あり)

-

Photo12:一番下のPackage Footprintの表示は互換性を示すもので、例えばGen1のZU29DRはそのままGen2のZU39DRやGen3のZU49DRに移行が可能という事になる

このGen3では6GHz帯までの信号に対応できるため、5G NR-Uでも外付けのADC/DACが不要になるという訳だ。

ちなみにRFSoCを利用する事で、例えばCA(Carrier Aggregation)の様に複数チャネルの信号を同時に扱うような場合であっても、そもそもアナログフロントエンドまで統合されているので設計・実装が容易に行える(Photo13)他、ミリ波帯についてもブロックコンバータこそ必要ながら、その先はRFSoCだけで実現できる(Photo14)とされている。

-

Photo13:Gen2では同時に2chのCAに対応しており、Gen3ではこれを8対まで同時に扱えるという話であった

-

Photo14:26GHz帯に関してはこんな感じ。一方60GHz帯については、もうすでに(それこそLattice傘下にあったSiBeamの様に)ディスクリート製品がいくつもあるため、顧客はそうした製品をベースに使うのではないか、という話であった

なお、Gen3に続く製品は、2018年開催のXDFで発表されたVersal AI RFとなる。ただ5Gの普及の状況からすると、まずは現在のGen1 RFSoCとこれに続くGen2/Gen3のRFSoCで5Gの基地局(主にエッジ側というかRRH:Remote Radio Head側)の実装には十分という話で、Versal AI RFは時期的に言ってもおそらく最初の5GのDeploy(実装)が済んだ後あたりのマーケットを狙っていると考えられる。