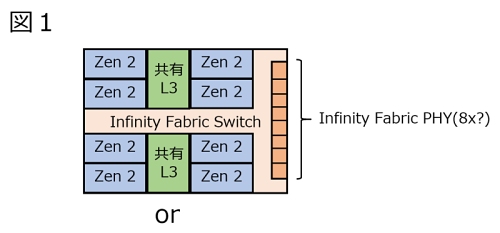

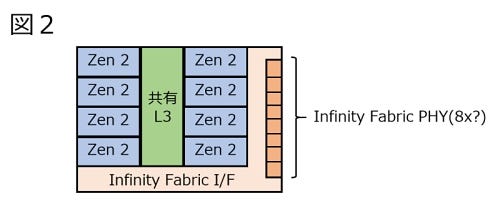

そのZen 2を搭載するダイの構造であるが、実は筆者は現時点でも図1なのか図2なのかの見極めがつかない。CPU側のダイはCPUとL3、それとI/Oチップと接続するためのInfinityFabricのI/F(およびPHY)から構成されるのは間違いないと思う。問題は、従来のCCX(Core Complex)の形を踏襲するか、それともCCXを拡張するか、である。

純技術的に言えば図2、つまり1つのCCXに8つのZen 2コアが格納されるほうがしっくりくる。図1のほうだと、2つのCCXをまたいでのコア間通信は、Infinity Fabric Switchを経由することになり、これによりLatencyが大きくならざるを得ない。従来のZenコアがまさにこれであるが、性能的にはハンデとなる。

そもそもZenの世代では何でCCXが4コアだったかといえば、8コア(Summit Ridge)と4コア(Raven Ridge)という2種類のダイを作るつもりがあったから、という話であり、なのでCCIXは4コアを基本にするのが妥当だったわけだ。

ところが今回はそもそも4コア製品を作るつもりがあるかどうか、というレベルで謎。今回のようなMCM構成を取るのであれば、4コア製品は8コアのうち半分を無効化して出しても良いわけで、そうすると4コアでCCXを構成するメリットはほとんどないことになる(実際には、欠陥などで8コアフルに使えないダイもそれなりにあるはずだから、無駄というほどではないだろう)。

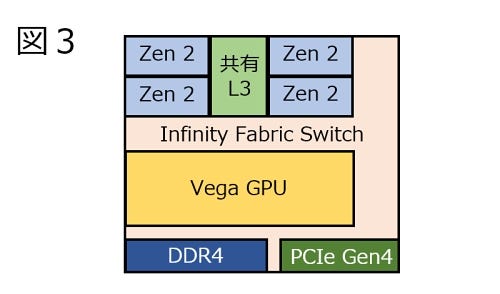

ただ読めないのは、GPU統合製品(つまりRaven Ridgeの後継)について、CPUとGPUを1ダイ化する(コスト的にはこれはあり得る)という決断をしていたとすれば、やはりCCXは4コアのまま、という可能性もある。

仮にGPU統合製品が1ダイ化する方向だとすれば、その構成は図3のようになると思われる。現行のRaven Ridgeとほとんど差はない。チップセットとはPCIe Gen4での接続だろう(GPUが別ダイの場合は後述)。どちらになるのか、現状そこまでは読み切れないというのが正直なところだ。