Next Horizonはあくまでもサーバー向け製品のイベントだったので、コンシューマ向け製品に関しては言及がなかったが、ここまで情報が分かっていると、推定は比較的容易である。とはいっても、Ryzen Gの7nm世代だけがちょっと難しい。可能性としては以下が考えられる。

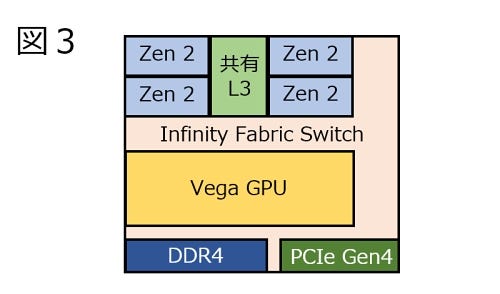

(1)GPUとCPUを1ダイで作りこむ(図3の方式)。このケースだと、7nmのダイを2種類(GPU統合と非統合)作る必要はあるが、これは14nm・12nmと同じシナリオである。この方式の問題点は、そこまで7nmの製品のラインナップを増やす余地があるかどうか、というあたりだ。

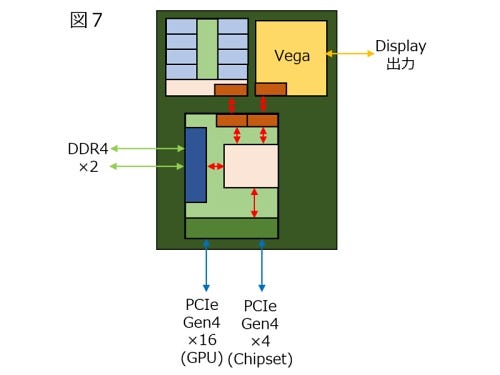

(2)GPUを7nmのDiscreteチップとして、MCMの形で実装する形態。Radeon RX Vega Mに近い構造である。もともと今年のCESで、Radeon RX Vega Mobileは言ってみればDiscreteチップの形で発表されており、これを統合する形だ。

ただ7nmプロセスへのシュリンクで、ダイサイズは半分ほどに減っている計算だから、可能性としてはあり得ると思う。実のところ7nm世代も、次回説明する64CUのVega 20だけでなく、CUを半分くらいに減らしたモデルもラインナップされると思われるから、このあたりを流用すればいいことになる。

(3)I/OチップにGPUを統合する形態。Raven RidgeからCPUコアを抜いて、その代わりにCPU接続用のInfinity FabricのPHYを統合するようなイメージ。作りやすさで言えばこれが一番かもしれないが、問題はこの場合それほどCU数を増やせないことと、設計は7nm Vegaではなく従来のVegaベースになること。このあたりがネックとなる。

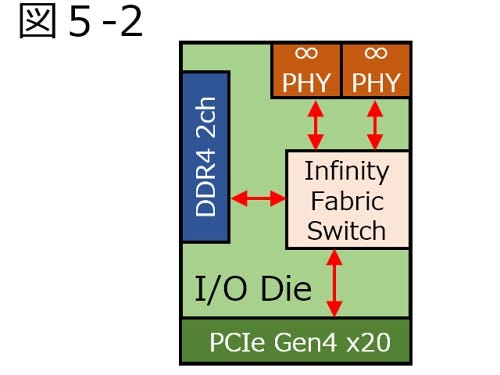

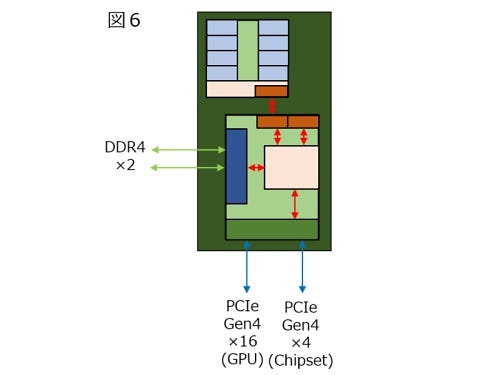

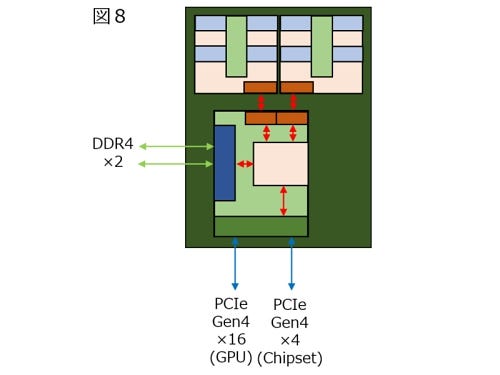

上記(1)と(2)の場合、Ryzen向けのI/Oダイの構造は図5-2のようになると想像される。接続されるダイは1個ないし2個だから、Snoop Filterの必要もL4 Cacheの必要もない。Southbridgeの機能はチップセット(それこそX470だのB450だの)があるから考える必要もなく、あとはPCIe Gen4(グラフィック接続用のx16と、チップセット接続用のx4)、メモリコントローラが2chあれば済む計算だ。

これが正しいとすれば、従来のGPU非統合のRyzen 3~7は図6のような構成になる。一方、グラフィック統合製品については、仮に(2)の方式だと図7のようになる形だ。(3)の方式の場合、I/OダイにVegaが統合されるから、構図としては図6と一緒だ。

あと、もう一つ製品ラインナップが用意されるかもしれない。それは図8のような構成だ。「16コア?」と思われそうだが、各ダイあたり4コア動作で、合計で8コアという構図になる(メモリが2chだとそもそも8コアを超えてもあまり意味がない)。

では何で2ダイ構成とするか?というと、これはプロセスの話に戻る。先に「計算で言えばBase 4.6GHz・Turbo 5.4GHz近くまで引き上げられることになる」と書いたが、実際にはここまで上げても安定動作は難しい。消費電力ではなく、発熱の問題が絡んでくるからだ。

7nmにすることで、ダイサイズは概ね1/3になった。ダイの組成そのものはシリコンをベースにしているから、比熱そのものはほぼ同じと見なしてよい。となると、面積が1/3ということは、熱容量も1/3である。つまり同じ消費電力だと、3倍温度が上がりやすくなる計算だ。従来よりも容易にThermal Throttlingが発生しやすくなると想像される。

これへの対策は、根本的には冷却を強化する(TIMをさらに効率の良いものにする)あたりしかないが、それとは別に状況を緩和する方策として「熱容量を増やす」という手もある。要するにダイサイズを増やせばよい。

CPUダイを2つにして、それぞれ半分しかCPUコアを稼働させなければ、熱容量は倍になる計算だから、Thermal Throttlingに入りにくくすることができる。また、L3の容量が倍になるから、性能の底上げにも役立つ。

こうした製品が出てくるとすると、ポジションとしてはRyzen 7のハイエンド、もしくはRyzen 9とかになるのかもしれない。まだそうした製品が出ると決まったわけではないが、必要ならばこうした製品を後追いで投入する余地が、図5-2の構成ではあることになる。こうしたマージンはAMDにとって必要だろうと思う。

恐らくRomeの出荷が一段落する来年(2019年)の4月ごろまで、7nm世代Ryzenの話はお預けだとは思う。こんな感じで色々想像できる余地があるのは(筆者にとって)非常に楽しい。あとは、実際の製品が順調に出てくれることを祈るのみだ。