日本シノプシスは6月13日、都内で開催した大規模ユーザー会「Synopsys Users Group(SNUG) Japan 2018」を開催。同イベントにて、バーチャル・プロトタイピングを使ったAIアクセラレータ設計とSoCへのインテグレーションについての説明を行った。

近年、ディープラーニングの活用に注目が集まり、GPUやFPGAを活用するアクセラレータのみならず、IT企業をはじめとしたさまざまな企業が、ニューラルネットワークのアルゴリズムを高速に実行するための専用プロセッサの開発など行うようになってきた。

こうした中、AI(人工知能)をとりまく状況としては、何を認識するのか(画像、音声、その他)、その対象に対して、どのようなニューラルネットワークが適切なのか(DNN、CNN、RNNなど)、またそうしたニューラルネットワークに対する柔軟性をどこまで持たせるのか、といったことを性能を発揮させるためには考える必要がでてきた。さらに、現在、AI分野は、次々とニューラルネットワークのアップデートや、新たなアルゴリズムなどが考案される状態となっており、そうした最新の情勢をどこまでキャッチアップして盛り込むか、といった部分もハードウェアを構築する上では考える必要があるという。

ディープラーニングに対応可能なアーキテクチャ

ひとえにディープラーニングを処理するプロセッサといっても、さまざまなアーキテクチャが存在する。主なものとしては、「CPU」「GP-GPU」「Enhanced GPU」「FPGA」「Vector DSP」「ASIP(Application Specific Instruction-set Processor:特定用途向けプロセッサ)」といったところだが、問題は適用場所で、データセンターやクラウド上で用いられる「学習」であれば、32ビットの浮動小数点演算が処理できれば、リアルタイム性なども考慮する必要がないので、CPUであろうがGPUであろうが、GoogleのTPUのようなASIPであろうが、問題はない。一方、エッジデバイスで活用されることとなる「推論」では、演算性能と消費電力の両立が鍵であり、精度してはデータ精度を落としても、あまり影響しないということで、半精度浮動小数点演算(FP16)や8ビット整数のINT8での積和演算などが活用されるようになっていることから、用途に応じた正しいアーキテクチャを選択することが重要だとする。

ASIPとしては、SynopsysもCNNエンジンを搭載することで、GPUとほぼ同等のパフォーマンスを数分の一の消費電力で実現することが可能な「EV6ファミリ」などを提供しているが、こうしたIPを活用する場合、データバンド幅を高くすることはもちろん、SoCの埋め込みでは、他の機能ブロックに影響を与えないかを考慮する必要があるほか、どういったツールフローで検討するかも重要になるという。

ハードウェアとソフトウェアの協調設計をいかに実現するか

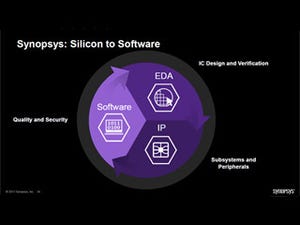

Synopsysは、ユーザーのAI開発早期化の実現に向け、仕様書からソフトウェア開発の短縮に着目したソリューション群の提供を行なっているという。

例えば、SystemCモデルのシミュレータであり、ハードウェアを機能レベルで表現することでバーチャルプロトタイプを可能とする「Virtualizer Development Kit(VDK))。これに、ルネサス エレクトロニクスやNXP Semiconductorsなどのプロセッサベンダのライブラリを組み合わせることで、仮想環境で開発を進めることで、開発の前倒しを可能とする。

また、重要となるのは性能および電力解析を早期に実現することだが、そのために仮想プロトタイピング環境「Platform Architect MCO」に2017年よりタスクグラフ生成機能を追加しており、これにより再現すべきデータフローをタスクレベルの並列性と依存性に注目する形で実行することが可能となるほか、各タスクが、どの程度の頻度でメモリにアクセスするのか、といった統計情報も見ることができるようになる。さらに、既存アプリケーションから次世代アーキテクチャを検討するためのワークロード・モデルを生成する際に、CaffeやTensorFlowといったフレームワークと連携させることで、その後は、パラメータの調整だけでAIのパフォーマンスを検討することができるようになるという。

自動運転に向けて進むバーチャルプロトタイプ

こうした活用はすでに海外、特に自動車分野では欧州を中心に積極的な展開が進んでいるという。例えばBoschでは、ティア1、システムメーカーとしての観点からのADAS SoCのアーキテクチャの課題の洗い出しにタスクグラフを用いてモデリング。インターコネクトおよびDDRメモリサブシステムを横断するトラフィックの性能解析を行い、こうした結果を外部のSoCサプライヤへのインテグレーションガイドラインの策定などに活用しているという。

また、Intelに買収されたMobileyeでは、Platform Architectを用いて、EyeQ5のSoCプラットフォームを構築するにあたって、各ベンダのIPを組み合わせたプラットフォーム上でソフトウェアを稼動させ、パフォーマンス解析を実施。どのようなコンフィグとアクセラレータIPがよいのかの探索に活用したという。

なお、同社では、Platform Architectを活用することで、消費電力との兼ね合いからメモリの種類を変更したり、インターコネクトのスループットを引き上げた場合の際のパフォーマンス変化なども見ていくことができるなど、詳細な開発を行なうことができるようになるため、電力の制約を守りつつ、パフォーマンスの最大化などを図っていくことができることを強調していた。