DynamIQとbig.LITTLEは何が違うのか?

さて、発表会の説明はこの程度にしておき、もうちょっと内部の詳しい話を2人のIanにお伺いした(Photo11)。

|

|

Photo11:左がIan Hutchinson氏(Director of Channel Marketing, Media Processing Group)、右がIan Smythe氏(Senior Director, Marketing Program, CPU Group) |

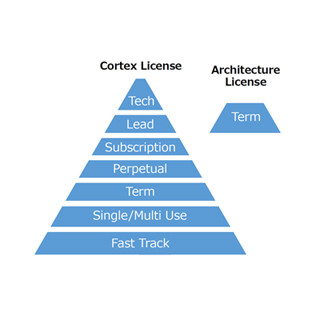

そもそもbig.LITTEとDynamIQの根本的な違いは何か?というと、CPUの制御切り替えの際の手法である。big.LITTEは図1のように、1つのインターコネクト(Interconnet)に2つのCPUクラスタが搭載されており、両方が同時に動くことは原則としては考えていない(もちろんApplication Aware Schedulingなどの話もあったが)。

この結果、例えばまずLITTLE側が動作していて、負荷が高まってbig側に処理を移す場合、

- big側のCPUをEnableにする

- LITTLE側のCPU Contextをbig側にコピーする

- LITTLE側のL2の内容をbig側にコピーする

- LITTE側をDisableにする

という4段階の処理が必要になった。逆も同じである。実はこの4つの中で一番手間が掛かるのが、L2の内容のコピーである。

そこでDynamIQでは図2の様に、L2をコアから切り離し、共有L2として実装することにした「らしい」。らしい、というのは「まだ特定の将来の製品に関する話は出来ない」(Smythe氏)という事だからだが、少なくともL2の内容の転送はDynamIQでは発生しない模様だ。

どうしてこれを今まで実現できなかったかといえば、既存のCortex-Aコアの設計はいずれもDedicated L2を前提にしたものだったからである。そのためCortex-Aコアそのものに手を入れる必要があった。big.LITTLEはあくまで既存のコアを利用してのコントロールスキームであったが、このままだとプロセッサ切り替えのオーバーヘッドが大きすぎる。1つのアイデアはL2をなくす、もしくは容量を削減することだが、これは性能に多大なインパクトがあるから現実問題として不可能である。そこで、次世代のコアからは共有L2(や、おそらく共有L3)を利用可能にするという設計方針が立てられ、この共有L2をサポートするCPUのコントロールスキームとしてDynamIQが生まれた、と考えるのが正しい様だ。

本当にDynamIQでADASやAIのニーズに対応できるのか?

ちなみにDynamIQでは現状、CPUが8個までに限られている。これは恐らくは共有L2側が、これを超えると大幅に性能が落ちるというあたりではないかと筆者は考えている。一応ARMにとって現在も主戦場であるモバイル向けには8コアあれば十分だから、というのも1つの理由になるだろう。ただクラウドサーバなどには全然足りないが、これに関しては「例えば先日発表したCMN-600などを使えば、複数のCPUクラスタ同士を接続できるため、問題ない」(Smythe氏)との話。この場合、図2の上半分+共有L2が、システム的には1つのCPUクラスタとして見える形だ。この複数のCPUクラスタがシステムに存在する場合、DynamIQはクラスタ全体をまとめて1つで制御するのか、それとも個別のクラスタごとに制御するのかを確認したところ、クラスタごとになるという話であった。これはちょっと既存のOSでは扱いが難しい(システムをNUMAとして扱えば不可能ではないだろうが、今度はメモリハンドリングがちょっと厄介になりそう)が、製品が投入されるまでにはまだ時間があるので、色々手を打ってくるのでないかと想像される。

ちなみにそういう訳なので、既存のCortex-Aプロセッサは基本的にDynamIQとは互換性がない。これに関してははっきりと、今後出るCortex-Aプロセッサのみが対象だと明言された。そしてADASやAIに関しての絡みであるが、まずAIに関して言えば今後のCortex-AプロセッサにはAIに関する新しい命令が追加されるはずで、これによる高速化も先の数字には入っているようだ。一番考えやすいのは8bit Integer(INT8)を利用したSIMDが追加される可能性だが、そのあたりは将来の製品計画になってしまうということで明確な回答は得られなかった。またADASに関して言えば、別にDynamIQでプロセッサの冗長性を確保できるようなスケジューリングスキームを提供するとかいう話はまったくなく、単にADASシステムで要求されるシビアな応答時間にbig.LITTLEでは対応が難しかった(主にL2の転送時間が掛かりすぎで)のが、DynamIQでは原理上これが削減できるので、ADASシステムでも利用できるレベルが期待できる、という話である。またbig.LITTLEよりもコアの構成に柔軟性があるので、例えばbig×6、LITTLE×2といった構成も可能であり、こうした場合にはより高い性能を発揮できることになる。これによりADASシステムで求められる、高いプロセッサ性能を提供できる、という話であった。

そのためDynamIQの対象はCortex-Aプロセッサのみで、Mali GPUやCortex-R、Cortex-Mプロセッサは対象外との事。これは当然といえば当然かもしれない。

今回の話は、まだコントロールスキームだけの話で、実際には次世代のCortex-Aプロセッサが出てこないとあまり意味はないのだが、これに関してはそう遠くない時期であることを匂わせており、5月末に開催されるCOMPUTEX TAIPEI~11月のARM TechConあたりで何かしらのアナウンスがあるのではないかと思われる。