「従来と同じやり方では実現できなかったので、新たな方式を考案した」(高野氏)のが、今回のメモリ積層型CMOSセンサーだ。

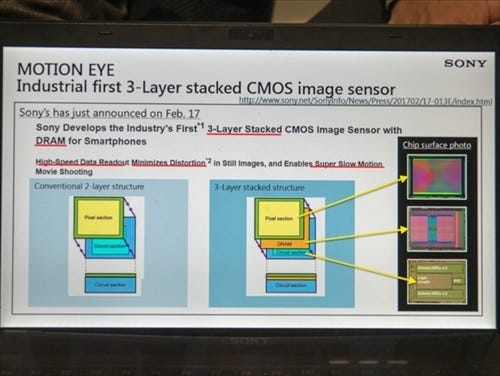

チッププロセスとして積層しているため、ほぼセンサーと同サイズのDRAMを積むことができ、従来の方式では搭載できなかった大容量メモリを搭載できたのが大きなポイントだ。「半導体の学会で発表するぐらいの難しい技術」と高野氏は言う。

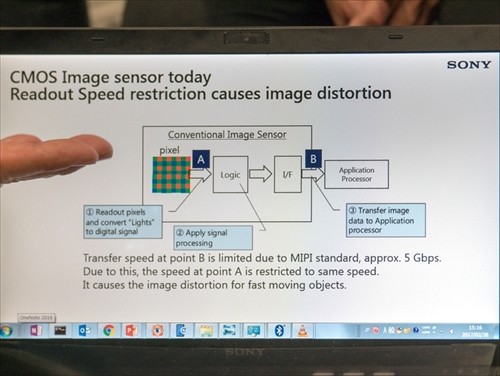

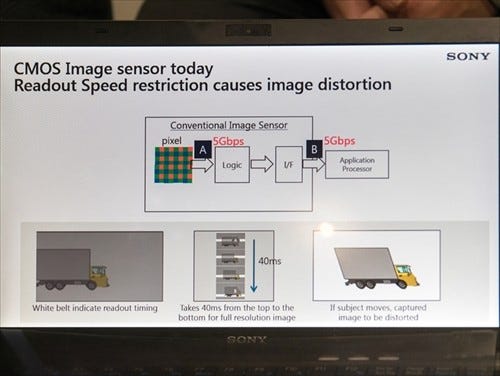

これによって実現される機能は、基本的にはRX100などと同等だ。そもそもCMOSセンサーは1列ごとに画素を読み出していく方式のため、最初の列と最後の列で読み出し時間がわずかにずれている。これが40ミリ秒であり、高速で動く被写体を撮影した場合などに像が歪む、ローリングシャッター歪みの原因となる(メカシャッターがないカメラの場合)。

|

|

ローリングシャッター歪み発生の原理。そもそもセンサーからロジック、アプリケーションプロセッサにいたる伝送速度は、5Gbpsと決まっている。フル画素の読み出しに40msかかるため、これより速い速度で移動する被写体は歪んで記録されてしまう(ローリングシャッター現象) |

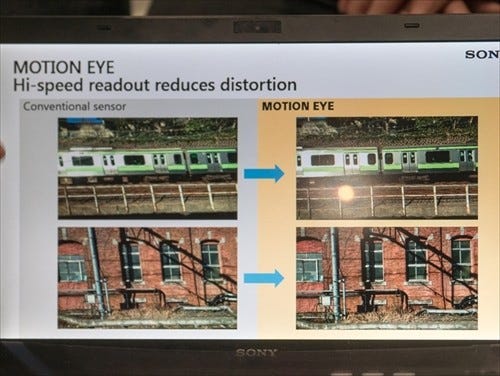

メモリ一体型CMOSセンサーでは、このメモリに高速で読み込みを行うことで、一気に読み込みが行われ、ローリングシャッター歪みが事実上発生しない。この仕組みはメモリ積層型CMOSセンサーでも同様で、メカシャッターのないスマートフォンカメラでは原理的に発生が避けられないローリングシャッター歪みを抑えることができるようになった。

さらに、画像読み出しでアナログからデジタルに変換する際に使われるA/Dコンバータは、従来2段の並列処理だったが、これを4段にしたことでさらに高速化を達成。DRAMを積層しただけではなく、さらなる高速化の仕組みが盛り込まれているのも特徴だ。