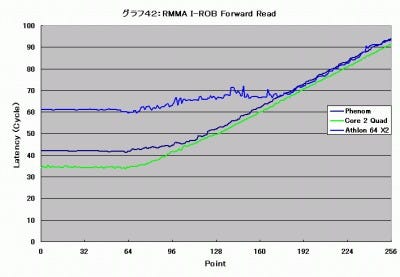

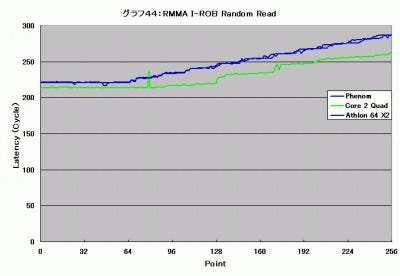

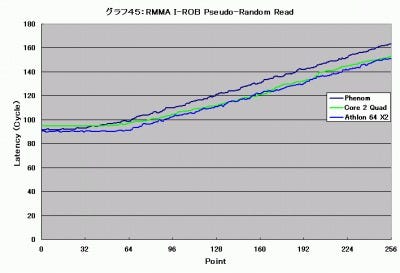

ここでちょっと趣向を変えて、このTLB Cacheが命令実行にどの程度のインパクトがあるかをROB(Re-Order Buffer)の性能から見てみた。グラフ42~45はRMMAのI-ROB Depthテストの結果である。このテストはRe-Order Bufferにどれだけの命令を蓄えられ、そこから溢れた場合にどれだけのLatencyでリカバーできるかという指標を与えてくれるもので、以前もこちらなどで実施しているから御馴染みの人も多いだろう。

結果を見ると、PhenomではこのROB周りを大幅にBrushUpした事が見て取れる。流石にRandom Readとなると大差無いが、Forward/BackwardではかなりCore 2 Quadに近いところまで改善しているからだ。

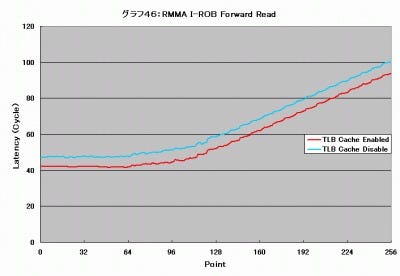

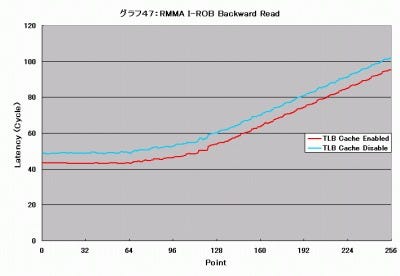

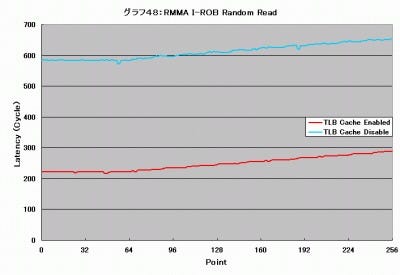

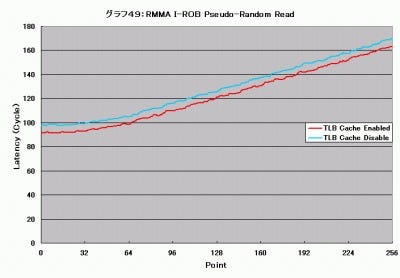

で、この状態でTLB CacheのEnable/Disableを行った場合にどうなるか、というのがグラフ46~49である。

平均して10Cycle程度スコアが悪化しており、折角Athlon 64 X2から改善した分の大半が帳消しになってしまう事に加え、特にRandom Accessのグラフ48では400cycle近くスコアが悪化しており、猛烈に性能面にインパクトがありそうな事が想像される。まぁ現実問題として、ROBにRandom Accessが激しく掛かるというプログラムが想像しにくいから、ここまで性能が悪化することはそう無いと思いたいが、最終的なアプリケーションパフォーマンスは相当悪そうだ、と考えられる。