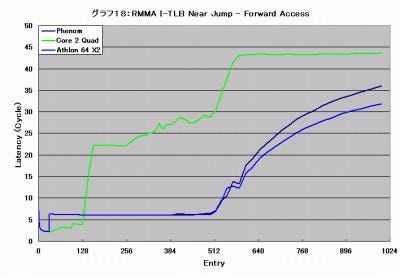

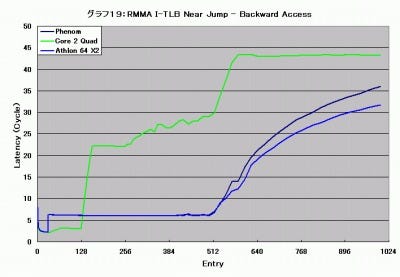

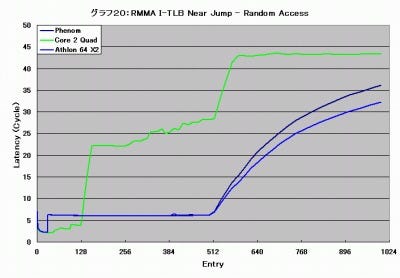

さてそのTLBの性能であるが、やはりRMMAをつかってちょっと確認してみた。まずグラフ18~20は、Near JumpでInstruction TLBを引く場合のLatencyの比較である。

Core 2 Quadの場合、I-TLBは4-way 128Entryの1段構成なので、128Entryを超えたあたりから急激に悪化する。とはいえ、20Cycle強で一度落ち着くあたりは、これを外すといきなりMemory Accessになるのではなく、ある程度キャッシュが効いている事を物語る結果になっている。恐らくPTE(Page Table Entry)あたりがL2に入っており、ここから引っ張る形でカバーしているのではないかと想像される。対するPhenomとAthlon 64、まず32EntryのL1 I-TLBにHitする範囲では効果的だが、その後L2 I-TLBになるとLatencyが概ね6Cycle(L1 I-TLBだと2Cycle前後)まで悪化する。ただそこから先はL2 I-TLBの512Entryまでほぼ一定、そこから次第に悪化する。面白いのは、Near Jumpに関しては512Entry以降のLatencyが、Athlon 64 X2の方が少ないことだ。

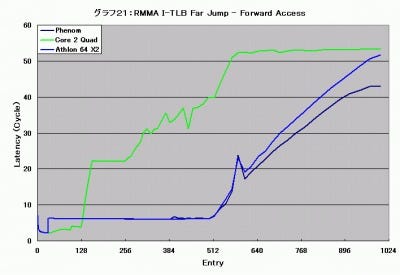

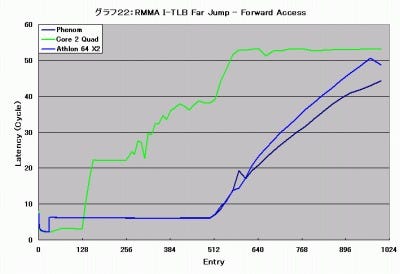

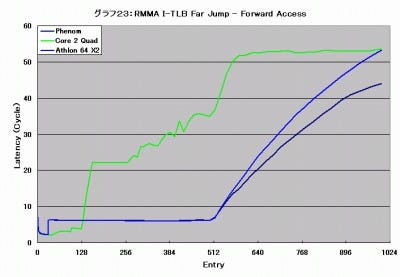

もっともこの傾向、Far Jumpになると一転する。グラフ21~23であるが、Core 2 Quadは概ね変わらず(Latencyの絶対値そのものは大きくなっている)。ところが512 Entry以降の数字を比べると、今度はPhenomの方がAthlon 64 X2よりもLatencyが少なくなっている。Near JumpよりもFar Jumpを重視する、というPhenomの傾向は、Photo08にも出てきた大量のメモリが搭載された場合の性能改善に繋がる部分であり、非常にわかりやすい。

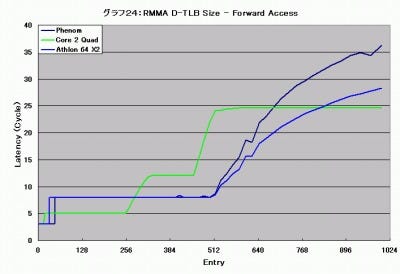

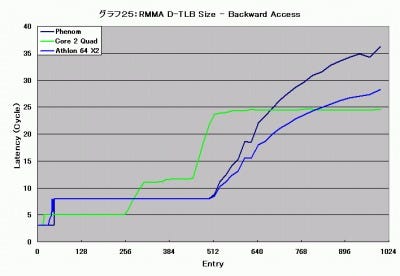

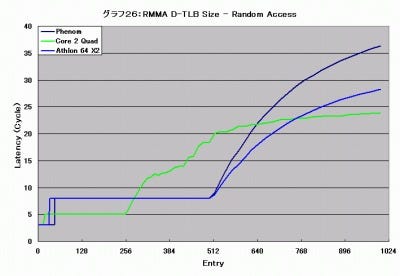

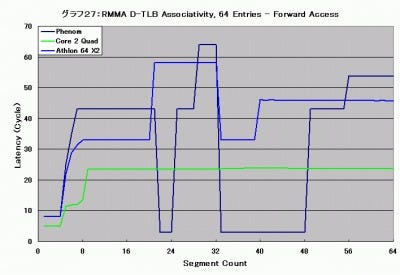

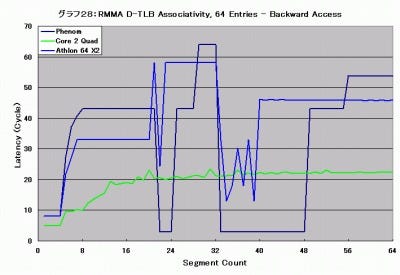

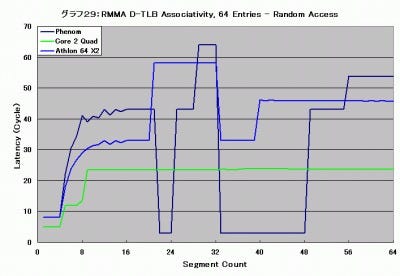

一方Data TLBであるが、アクセスするEntry数を普通に増やしてゆく限りにおいて、傾向(グラフ24~26)はI-TLBのNear Jumpに近い。面白いのはここからだ。PhenomやAthlon 64 X2のTLBの場合、L1はFull-associativity、L2が4-way set associativityとなっている。Core 2 Quadは8-way set associativeであるが、これがどのように影響するかを見たのがグラフ27~29である。

この場合は64entryと小さいエントリ数に限ってのテストだから、本来ならば全部綺麗にHitしても良さそうなものだが、実際はさにあらず。ごらんの様に細かく変化する。面白いのはCore 2 Quadがほぼ一定の値を取ることで、むしろFull-associativityがネガティブな方向に作用している事が判る。もっとも、この値はPhenomやAthlon 64 X2のスコアが一番激しくバタつくところを示しており、例えば16 Entryに限るとむしろCore 2 Quadが一番悪いスコアだったりするから、これだけを見て優劣は比較できないのだが。ただ、やはりIntelとは狙う方向性が異なっていることがここからも見て取れる。余談ながら、グラフ24で平均値を取ると、Phenomが31.4Cycles、Core 2 Quadが21.7Cycles、Athlon 64 X2が40.9Cyclesとなっており、細かいところでもPhenomが改良を施している事が判る。