テクノロジー分野の採択論文数トップは26件の韓国、日本は7件

VLSI Symposium 2025のテクノロジー分野には、349件の応募があり、このうち104件が採択された。採択率は30%だが、このほかLate News Paperとして9件の応募があり、そのうちの1件(SK hynixのDRAMに関する論文)が採択されている。

テクノロジー分野への投稿論文件数の地域・国別推移を見ると、今回、最多投稿なのは中国で109件、昨年から20件ほど増加している。次いで、韓国の66件、台湾58件とアジア勢が続いている。この数年の傾向だが、アジア地域からの投稿数が増加傾向にある。ただし、日本は14件で、前回の21件から7件の減少となっている。

テクノロジー分野への採択論文件数の地域・国別推移を見ると、今回の最多論文採択地域・国となったのは、昨年同様の韓国で26件であった。次いで、米国と中国が18件ずつ、その後、台湾の16件と続く。アジアからの採択件数は全体の71%を占めた。中国が昨年の9件から倍増させているが、日本は昨年の9件から7件に減少している。ただし、日本の採択率は50%と高い割合を示している。

産業界(研究機関を含む)と大学の応募件数比率は7:3だが、採択件数比率は5:5だった。企業からの論文の採択率は51%と高かったのに対して、大学からの論文の採択率は21%と低い結果となった。企業では、応募前に社内での審査や選別が行われているものと思われる。

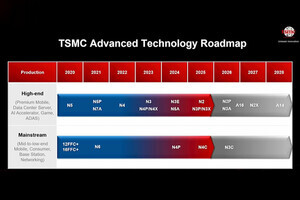

採択論文数を発表機関別で見てみると、トップはSamsung Electronicsの12件、2位はベルギーimecの10件、3位は国立シンガポール大学と中国の北京大学の各8件、その後は、5位にTSMCの6件、6位に国立台湾大学の5件と続いている。Samsungとimecは、昨年も2桁の論文が採択されており2強といえる。また、北京大学は、一昨年まではゼロ、昨年は1件であったことを考えると、8件採択された今年は大躍進といえるだろう。

日本からの論文の発表機関としては、東京大学が2件、キオクシアが2件、ソニー、産業技術総合研究所(産総研)、奈良先端科学技術大学院大学(NAIST)が各1件の合計7件である。

テクノロジー分野の注目論文

VLSIシンポジウム2025のテクノロジー部門について、VLSIシンポジウム委員会では11件を注目論文として紹介している。

今回は、このうちIntelとTSMCから発表された最先端CMOSロジックのプロセスとパッケージングに関する論文とソニーと北京大学から発表されたイメージセンサに関する論文の概要を説明したい。

Leading-Edge CMOS Logic Process

- Intel 18A Platform Technology Featuring RibbonFET (GAA) and PowerVia for Advanced High-Performance Computing,(リボン FET(GAA)とパワービアを適用した先端ハイパフォーマンスコンピューティング向けIntel 18Aプラットフォームテクノロジー) (論文番号:T1-1)

Intelからは、2025年末までに量産開始が計画されているIntel 18A(いわゆる1.8nmあるいは18Å)プロセス技術に関する発表が行われる。

リボンFET(いわゆるゲート・オール・アラウンド・ナノシートFET、GAA)とパワービア(いわゆる裏面電源供給)を適用したIntel 18A技術は、Intel 3(いわゆる3nmプロセス)技術と比較して30%以上の面積スケーリングとフルノードの性能向上を提供するという。

また、高性能(HP)および高密度(HD)ライブラリを備え、フル機能の技術設計能力と設計の使いやすさも向上させたとしている。

Advanced Logic packaging

- High-Density Wafer Level Connectivity Using Frontside Hybrid Bonding at 250nm Pitch and Backside Through-Dielectric Vias at 120nm Pitch After Extreme Wafer Thinning(250nmピッチのハイブリッドボンディングと120nmピッチの裏面絶縁層貫通ビアによる高密度ウェハレベル接続) (論文番号:T6-1)

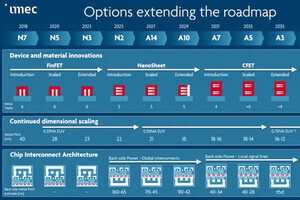

ベルギーの先端半導体研究機関であるimecは、高密度ウェハレベル接続性を250nmピッチのハイブリッドボンディングと120nmピッチの裏面絶縁層貫通ビアを用いて実証したことを報告する。裏面からの接続は基板薄膜化後にシャロートレンチアイソレーション層を貫通するViaを通して形成されている。

-

左が250nmピッチのFace-to-Faceでのハイブリッドボンディング接続のTEM像、真ん中がFace-to-Faceハイブリッドボンディングと裏面接続のイメージ図、右が絶縁層貫通ビア(TDV)を用いた裏面/表面間接続のTEM像

Image Sensor Technology

- A Back-illuminated 10 μm-pitch SPAD Depth Sensor with 42.5% PDE at 940 nm using an Optimized Doping Design(電子増殖領域の設計最適化と不純物分布最適化で波長940nmで光子検出効率42.5%を達成した裏面照射型10μmピッチ単一光子アバランシェダイオード(SPAD)センサー) (論文番号:T1-2)

ソニーセミコンダクタソリューションズは、300mm CMOSプラットフォームを用いた、裏面照射型構造を持つ10 μmピッチの単一光子アバランシェダイオード深度センサーに関する発表を行う予定。光子検出効率を向上させるために、電子増殖領域の設計最適化と不純物分布の最適化を実施し、波長940nmにて、世界最高レベルとなる42.5%を達成したという。

Image Sensor Technology

- First Demonstration of 1T FDSOI-based >1000fps Image Sensor with In-Pixel Computing(インピクセルコンピューティングを備えた1T FDSOIの1000fpsを超えるイメージセンサの初めてのデモンストレーション) (論文番号:T6-4)

中国の北京大学は、22nm FD-SOIテクノロジーで製造した1T画素構成を有する画素数128×128のイメージセンサの提案を行う予定である。

埋め込み酸化層の下側に形成する空乏層を受光層に適用することで光感度を持たせたという。主な特徴として、(1)FETの増幅機能を用いることで5×105A/Wと高い受光感度が得られること、(2)ゲート、ドレインに印可する電圧によって受光感度を調整可能であり、1T画素構成でありながら画素内のコンピューティング機能を持たせることができること、(3)設計・製造したチップでは、画素内信号処理機能と露光、信号処理、読出しのパイプライン動作によって、1000fps超のイメージングと特徴認識を実現していることが挙げられる。