「2020 Symposia on Technology and Circuits(VLSIシンポジウム2020)」は、2020年6月15日~18日(米国時間、日本時間は翌日)の期間で開催されたが、実はすべての講演の録画されたものが2020年8月末まで有料ながら視聴可能となっている。

従来のようなホテル会場でのリアルな会議の場合は、多数のパラレルセッションのなかで物理的に1つのセッションにしか参加できないが、バーチャルなオンデマンド形態では、希望すればすべてのセッションの講演を視聴可能である。このためには極めて長時間を要するため、多くの参加者の要望で有料会議登録者の視聴期間が8月末まで2ヶ月ほど延長されたようだ。

今回のVLSIシンポジウムは、テクノロジーシンポジウム86件、サーキットシンポジウム110件、合わせて約200件の一般論文の発表が、テクノロジー分野15セッション、サーキット分野23セッション、テクノロジー/回路合同分野で5セッションの合計43セッションで構成されていた。

テクノロジーシンポジウムでは、メモリ関係のセッションが最多で、NAND/NOR/PCM、RRAM、RRAM、FeRAM、STT MRAM、次世代MRAMなど、メモリの種類ごとにセッションがあった。先端デバイス/プロセス関連では、先端Si CMOS、先端プロセス、Ge/SiGeデバイス、量子コンピューティング向けデバイス、それに新規デバイス。このほか3D積層・実装関連が3セッションというような構成であった。

今回から数回に分けて約200件の一般講演の中から、前評判の高かった論文を、テーマ別にいくつか紹介していきたい。まずは、先端CMOS技術分野から、ベルギーimec、フランスLeti、米IBMの発表を紹介したい。

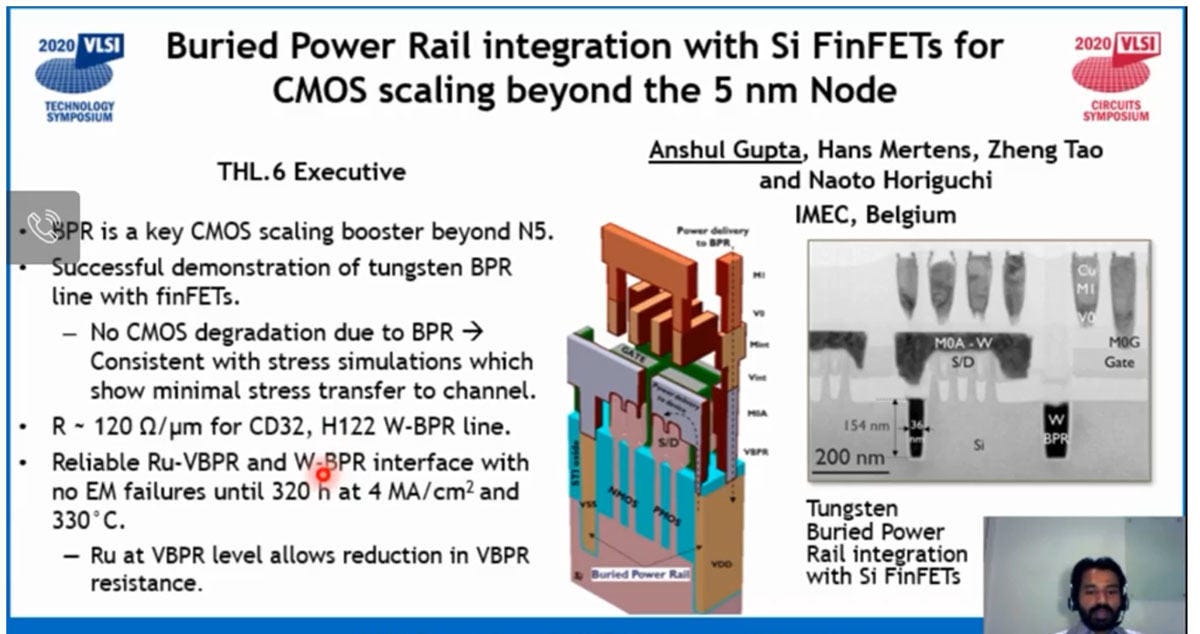

5nm以降の最先端プロセス向け埋め込み型配線技術をimecが発表

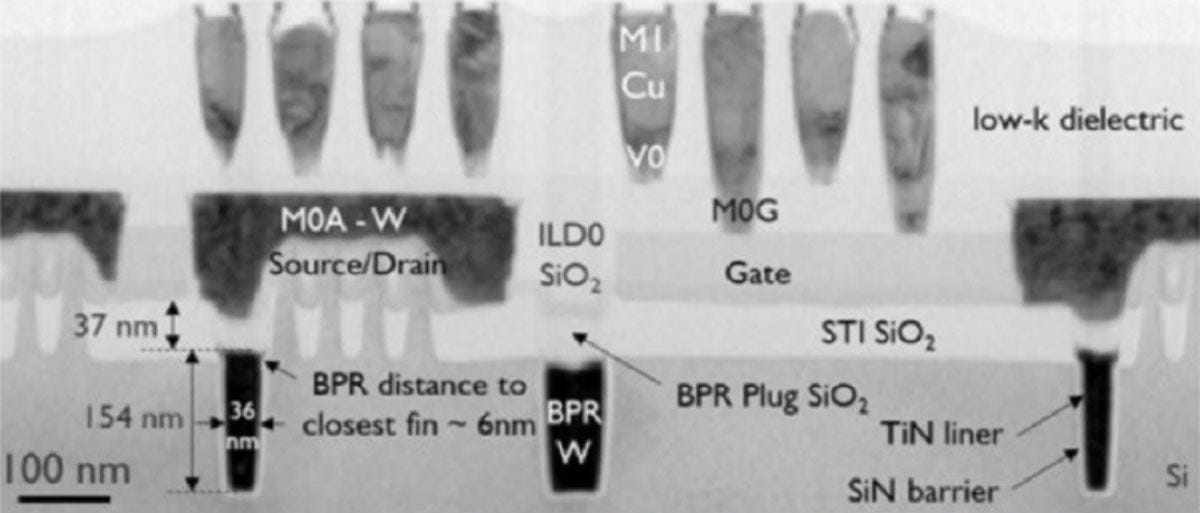

ベルギーの独立系研究機関imecの研究者らは、埋め込み型配線(BPR:Buried Power Rail)について、FinFET技術を用いて実証した結果を報告した。

この技術を5nm世代以降のスケーリングを維持する重要な技術として位置付けている。実証にはタングステン(W)を用い、この技術によるトランジスタへの影響がないことを明らかにしている。

さらに、タングステン埋め込み配線に接続するビアにルテニウム(Ru)を用いることで、4MA/cm2で330℃の条件下におけるエレクトロマイグレーションストレスにも320時間以上耐えることも確認され、低抵抗を実現するためにはルテニウムが同技術に欠かせない金属材料の候補であることを提案している。

-

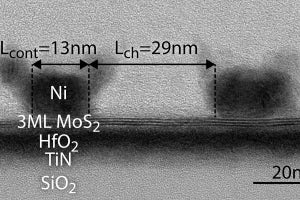

図2 集積化された埋め込みタングステン配線(BRP)の透過型電子顕微鏡写真。Si FinFETのフィンピッチは45nmでフィンとBPRの最小距離は約6nm (出所:VLSIシンポジウム予稿集、以下、図3、図4も同様)

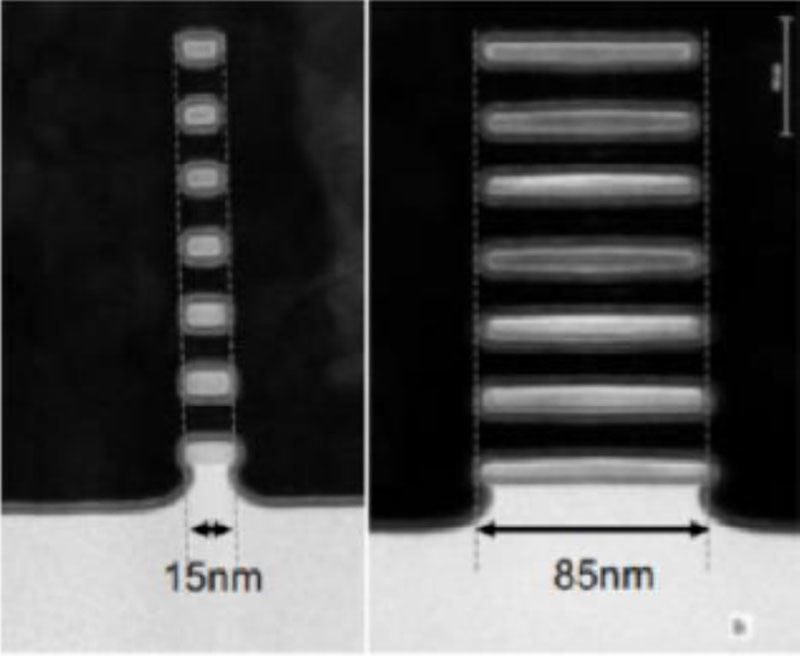

7層ナノシートGate-all-around(GAA)トランジスタをLetiが発表

Gate-all-around(GAA)ナノシートトランジスタは、その大きな有効チャネル幅によって、最先端のFinFETトランジスタと比較して高い性能を示す。

フランスの国立電子技術研究機関であるCEA-LETI-MINATECの研究者らは、デバイス性能を向上するための占有面積あたりの有効チャネル幅の増強と、製造プロセスの複雑性との間のトレードオフについて報告した。

彼らは初めて実験的に、置換メタルゲートとインナースペーサー、および自己整合コンタクトを使った7層構造のGAAナノシートトランジスタを試作した。作製されたトランジスタはチャネルに対する優れた電気的制御と非常に高い電流駆動能力を両立し、2層積層-ナノシートGAAトランジスタの3倍のドレイン電流を示したという(VDD=1Vで3mA/μm)。

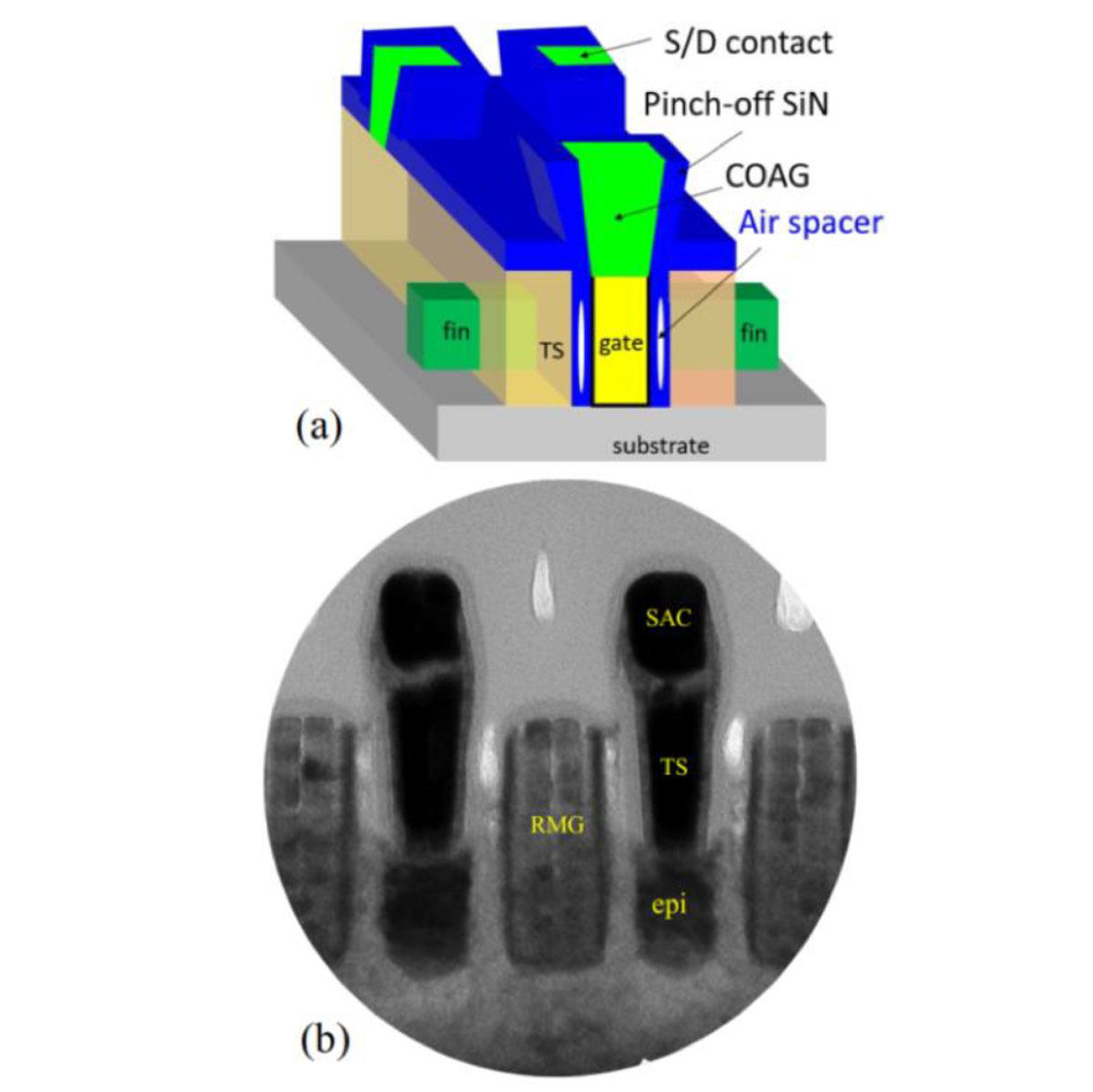

先端CMOSのエアスペーサ形成技術をIBMが報告

トランジスタにおけるゲート側壁の絶縁膜スペーサの一部をエア(空隙)スペーサにすることは、寄生容量を減らす効果的なアプローチとして以前より認識されている。

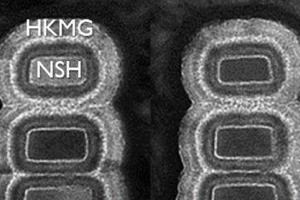

IBMの研究者らは、自己整合によるコンタクト(SAC)とアクティブ領域でのゲートコンタクト(COAG)を有するFinFETトランジスタに対しても十分適用できるよう改良されたエアスペーサ技術について報告した。

新しい集積化方法ではMOL(ミドル・オブ・ライン)コンタクト(SACとCOAG)形成後にエアスペーサが作られており、基本的なトランジスタ構造によらずエアスペーサを形成することが出来るため、FinFETやGAAに対してシームレスなエアスペーサの適用を切り開くものとなる。

これにより15%実効容量(Ceff)の低減効果を実証したとする。この新しいエアスペーサの適用により得られる電力や性能に対するメリットは、FinFETを7nmノードから5nmノードにスケーリングするよりも優れた効果が得られたという。

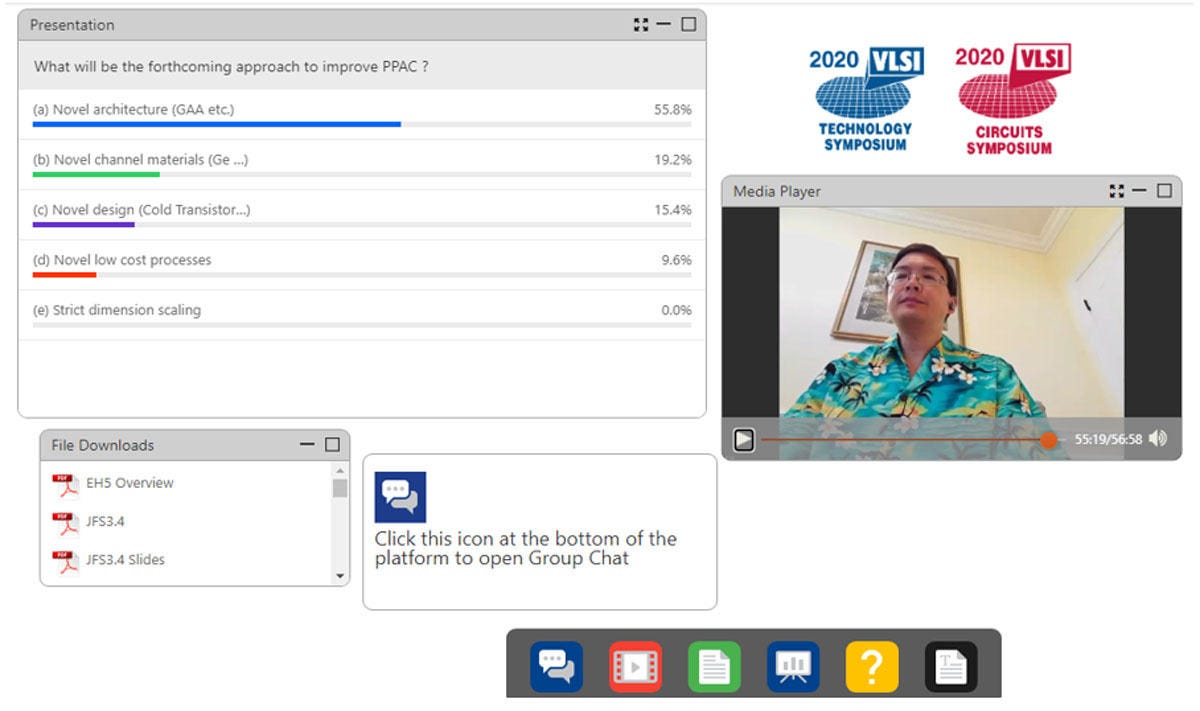

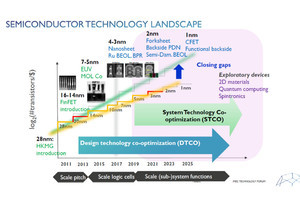

PPACを改善するための今後のアプローチは何か?

先端CMOS技術に関するライブセッションの最後に視聴者全員に対して「PPAC(電力、性能、チップ面積、コスト)を改善するために今後採るべき最適なアプローチはなにか?」という5択のアンケートが実施され、以下に示すような結果が得られた。

- GAAのような新しい構造の採用 55.8% (全回答者に対する割合)

- Geのような新しいチャネル材料の採用 19.2%

- Cold Transistorのような新しい設計も採用 15.4%

- 新しい低コストプロセスの導入 9.6%

- 厳密なパターン寸法の比例縮小 0%

というわけで、過半の参加者がGAAのような新しい構造への移行がPPACを実現する最適な手法と考えている事がわかった。なお、複数項目を選んだ回答者がいるので、合計は100%を超えている。