デジタルアプリケーションとデータ処理の急速な台頭により、コンピューティングパワーの需要は爆発的に増加している。 気候変動や食糧不足など、私たちの時代の主要な課題に取り組むために人工知能(AI)の使用が増えるにつれて、コンピューティングの必要性は今後6か月ごとに2倍になると予想されている。

指数関数的に増加する量のデータを持続可能な方法で処理するには、高性能半導体技術の向上が必要である。そのためには、5つの課題に同時に取り組む必要があるとimecは指摘している。世界中のどの企業も単独でこれを達成することはできない。半導体エコシステム全体にわたり、皆で一緒にイノベーションとコラボレーションに取り組むことにより、「ムーアの法則」を継続することができるとimecは確信している。この確信こそが、今後15年から20年先まで見通したimecの野心的なロードマップ(図1)からの重要なメッセージである。

今回のimec研究者自身が解説する先端半導体微細化研究は、現点に戻って、imecが策定した15年先まで見据えた半導体微細化ロードマップ策定の背景を解説したい。

次世代半導体開発に一度に5つの壁

高性能半導体技術を開発するためには、5 つの課題に同時に取り組む必要がある。それらは、

- スケーリングの壁:リソグラフィそのものによるスケーリング(比例縮小)は減速している。マイクロチップとトランジスタの個々の構造が原子のサイズに近づき、量子効果がマイクロチップの動作に干渉し始めるため、スケーリングはますます困難になっている。

- メモリの壁:システムパフォーマンスは、コアとメモリ間のデータパスの制限に直面している。実際、メモリ帯域幅はプロセッサのパフォーマンスに追いつくことができていない。1秒あたりのFlops数(1秒間に浮動小数点演算を何回できるかという能力)は、1秒あたりのギガバイト数よりも多いという現実がある。

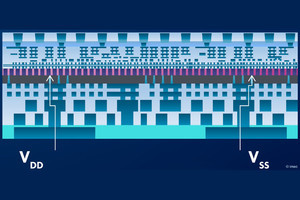

- 電源の壁:半導体チップに電力を供給し、チップパッケージから熱を抽出することがますます困難になってきているため、改善された電力供給と冷却の概念を開発する必要がある。

- 持続可能性の壁:半導体デバイスの製造は、温室効果ガスや水、天然資源、電力消費など、環境フットプリントの増加をもたらしている。この対策が必須となっている。

- コストの壁:明らかに、チップの製造コストは、設計およびプロセス開発のコストとともに、複雑さが増すにつれて爆発的に増加する可能性がある。

Grdon Moore(Fairchild共同創業者でその後、Intel共同創業)は、集積回路(IC)チップに搭載される素子の数は約2年ごとに2倍になると指摘した。いわゆる「ムーアの法則」と呼ばれる経験則である。この予測は、デナードスケーリング(当時IBMのRobert Dennardによって提唱されたMOSトランジスタの比例縮小測)とともに、従来のフォンノイマンコンピューティングアーキテクチャに固執して発展させるに際して特に当てはまる。

imecは、新たな微細化ロードマップの中で、アーキテクチャ、材料、トランジスタの新しい基本構造の根本的な変化などのパラダイムシフトを伴うチップ技術の未来のための代替パスを提案している。imecは、2年から2年半で継続的に世代交代し、7nm(2018年)から0.2nm(つまり2オングストローム、2036年)に進むロードマップをすでに発表している(図1参照)。

リソグラフィ技術の進歩でスケーリングを継続

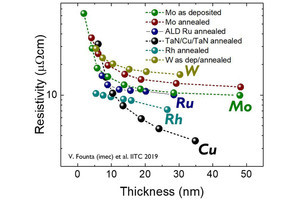

まず、リソグラフィの継続的な進歩がさらなる寸法スケーリングの鍵となる。従来のリソグラフィは光を使用しており、現在、光の波長はパターンに必要な精度よりも長くなっている。そのため、EUVリソグラフィが導入された。7nm以降の大量生産で使用されている。5nm世代から2nm世代へと微細化が進むにつれてますます多用されるようになる。さらに微細化するには、より大きな開口率を実現したEUVの最新バージョン、つまり高NA EUVが必要となる。これを実現するためのミラーでは直径1mにつき20pmの精度が必要となる。高NA EUV露光装置は、ASMLによって開発中で、最初のプロトタイプが2023年後半に利用可能になる予定である。大量生産への導入は、2025年または2026年の間に予定されている。製造への導入のリスクを回避するために、imecはASMLとともに、マスク技術や湿式または乾式UVレジストとして使用する材料、計測、光学特性評価など、すべての主要な構成要素を開発するための非常に集中的なプログラムを設定している。

(後編に続く)