前回は先端ロジックのスケーリングに向けて克服すべきトランジスタの設計上および物理上の制約を論じた。これを受けて、今回はICチップを構成する個々のデバイスに信号と電気を通す配線を取り上げ、その主なスケーリング課題について述べてみたい。

配線は、金属でできた2つの主要部分からなる。1つはデバイスの同一層内に電流を流すライン、もう1つは層間をつないで電流を流すビアである。配線ピッチが狭まるとラインとビアもそれぞれ幅が狭くなり、抵抗が高まるほか電気信号の遅延も大きくなる。さらに回路全般にわたって電圧降下が増え、回路速度が低下し、電力消費が大きくなる。

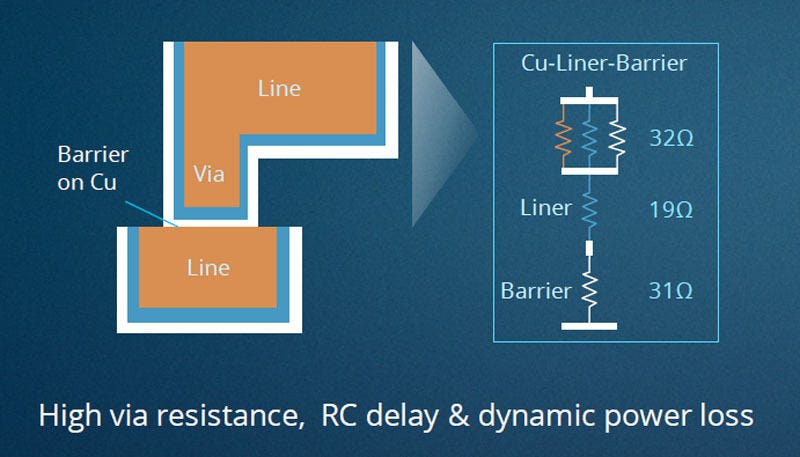

トランジスタの性能はスケーリングに伴って向上するが、これは金属配線には当てはまらない。むしろ寸法の微細化に伴って、配線のビア抵抗は10倍に増え得る(図1)。その結果RC遅延(配線抵抗R・配線容量C)が発生し、性能低下と消費電力の増加につながる。

配線はデバイスに供給される電力の3分の1近くを消費しており、RC遅延の75%以上は配線で発生する。したがってデバイス性能全般を向上させるには、配線抵抗を低減させることが最善の方法といえる。

抵抗の問題を放置しておくと、トランジスタ微細化による性能向上のメリットが相殺されてしまう恐れもある。

微細形状の配線抵抗を改善する鍵は、新しいメタルフィルプロセスを開発して高抵抗のバリアとライナーを極力薄くするか完全になくすことにある。これにより配線抵抗が低減するほか、充填される金属導体の体積を最大化する。

典型的な銅(Cu)配線構造は、3層で構成されている(図2)。まず絶縁材料からなる側壁上に窒化タンタル(TaN)のバリアが成膜され、接着性を強めるとともに絶縁膜へのCu拡散を防止する。次にコバルト(Co)ライナーが成膜される。CoライナーはTaNバリアに密着し、続くCuフィル(充填)を容易にする働きを持つ。そして最後に残った空隙にCuリフロープロセスでCuを埋め込む。

では、配線のさらなるスケーリングに必要なものは何だろうか。

ビア全体の抵抗に最も大きく影響しているのは、TaNとCuのインタフェースである。抵抗を減らす最善の方法は、このインタフェースを取り払ってしまうことだが、それを実現するには、選択的なバリア成膜プロセスの開発が必須となる。

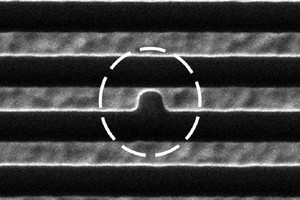

ライナー/バリアのアプローチには、もう1つ課題がある。微細化に伴ってビアの体積が小さくなると、ライナーとバリアが占有するスペースの割合が高まり、導体であるCu用のスペースが減少する、という点だ。その理想的なソリューションと見られるのが、まったく新しいCuリフロー技術である。

まったく新しいアーキテクチャがさらなるブレークスルーをもたらす

配線を2nmノード以降にスケーリングするには、デザインのさらなるブレークスルーが必要となる。そこで注目されるのが、どのようにトランジスタに電源を供給するかだ。

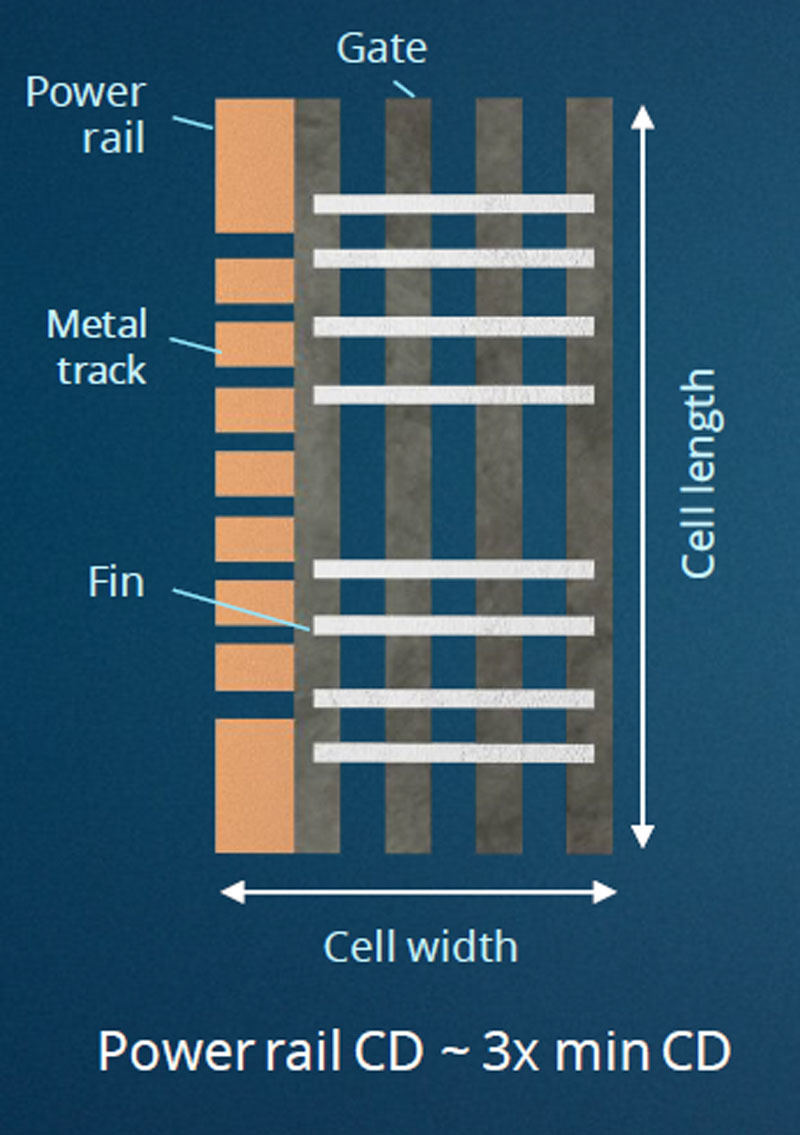

ロジックチップを構成する標準的なセルは、トランジスタと配線構造の集合体で、特定の論理機能を担う。これらのセルは、それぞれシグナルライン用のスペースとパワーレール(外部電源からトランジスタに電流を届ける線)を必要とする。パワーレールは一般に配線の最も細い線に比べて3倍も太いため、これがセルサイズに大きく影響する(図3)。

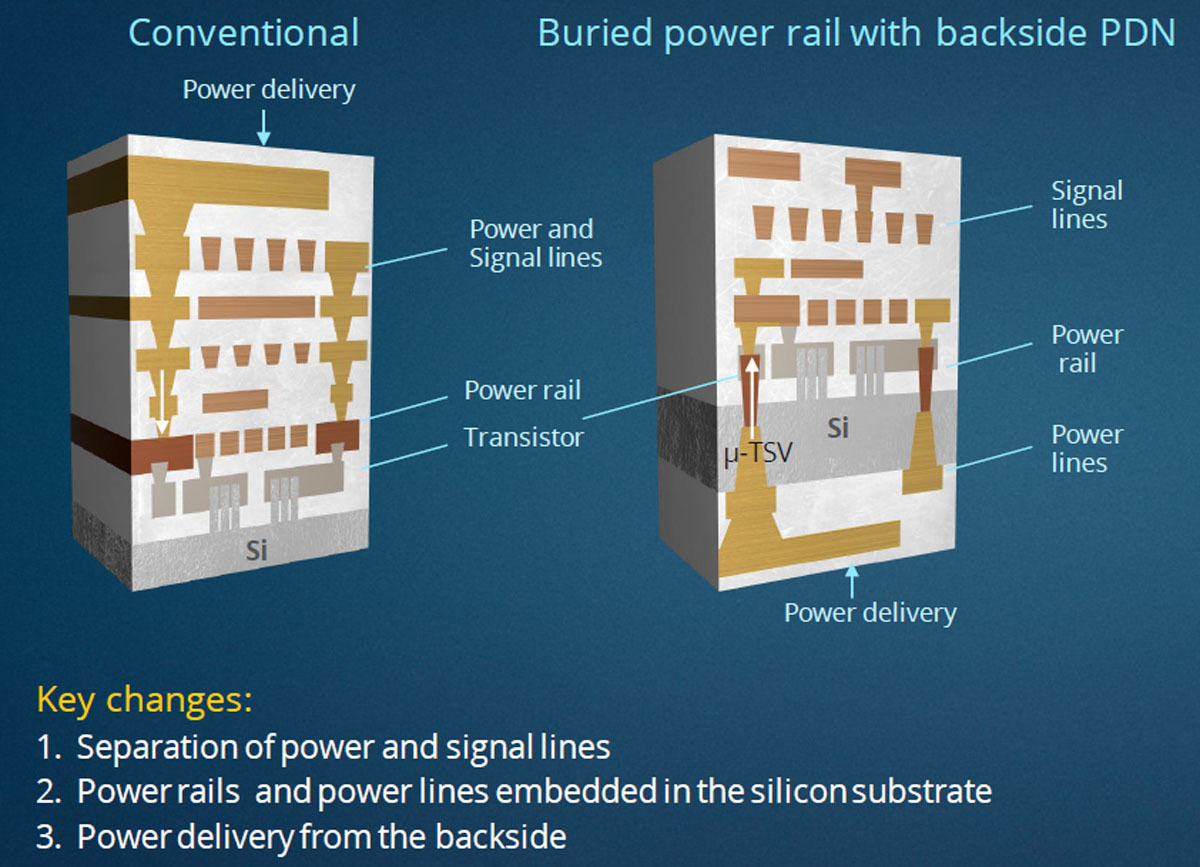

加えて、トランジスタへの電源供給ネットワークはチップのメタル層すべてを通る必要がある。メタル層の数はゆうに12を超えるので、各層での金属抵抗により供給電圧がかなり低下する。こうした累積的な電圧ロスが10%前後までは設計の工夫で対処は可能だ。しかし、微細化が進むたびに抵抗はさらに増していくため、新しいアーキテクチャを考案しない限り、やがて電源供給ネットワークが電圧の50%を消費してしまう可能性もある。

ロジックのスケーリングを継続させるため、業界では裏面電源供給ネットワークの埋め込みパワーレール(buried power rail)と呼ばれる新しいアーキテクチャの開発が進められている(図4)。 このアーキテクチャではトランジスタセルへの電源の供給を、シリコンウェハの裏側のトランジスタセルの下から供給する形をとる。この方式は3つの重要な利点を持つと見られる。電圧ロスが最大7分の1にまで抑えられること、トランジスタセルの面積が20~33%縮小できること、そして微細化で抵抗が高まるシグナルラインに対し、より多くのセルスペースを割り当てられることである。

まとめ

ロジックデバイスのPPACt改善には、トランジスタ、コンタクト、配線のイノベーションを同時に行う必要がある。

従来のアプローチは限界に達しつつあるが、すでに新しいマテリアルとマテリアルズ エンジニアリング技術を活用したソリューションも視野に入っている。AMATでもマテリアルの創出、改変、除去、解析の各分野で幅広い技術ポートフォリオを備えていることから、こうした技術を他の追随を許さないユニークかつ実効性の高い方法で組み合わせていく考えだ。

この連載はApplied Materialsが発行している英文ブログをアプライド マテリアルズ ジャパンが翻訳したものを一部修正して掲載しております。

著者プロフィール

Mehul NaikApplied Materials

マネージングディレクター 兼 セミコンダクタプロダクトグループ先進製品技術開発チームのテクニカルスタッフ主要メンバー

ロジックプログラム責任者として技術転換のマッピングに取り組むとともに、トランジスタと配線の部門横断プログラムを主導。

執筆した出版物は60以上、保有する米国特許は70件を超える。レンセラー工科大学で化学工学の博士号を取得。