半導体業界は転機を迎えている。IoT、ビッグデータ、AIなどがもたらす新たな成長の波を受け始めた今、半導体需要はこれまでになく高まってきた。しかしその一方で、ムーアの法則に沿った従来の2Dスケーリングの技法には限界が見えつつある。半導体メーカーが長らく依存してきたPPACt(消費電力、性能、面積あたりコスト、市場投入までの期間)の着実な改善が途絶えかねないのだ。この問題が特に顕著なのはロジックチップの分野である。ロジックはほぼあらゆるエレクトロニクス製品にメインプロセッサとして用いられ、高い電力効率と性能が求められるからだ。

この問題に焦点を当てるため、Applied Materialsでは6月16日(米国時間)に、AMATのエンジニアと業界各社の専門家たちによるPPACtの継続的改善に向けた課題とソリューションその他、ロジックスケーリングのロードマップについて意見交換会「Logic Master Class」を開催した。

取り上げた分野は、トランジスタと配線のスケーリング、パターニング、design technology co-optimization(DTCO:設計とテクノロジーの協調最適化)などである。これらの分野に共通しているのは、従来の2Dスケーリングを補う必要性から、新しいチップアーキテクチャ、新しい3D構造、新しいマテリアル、形状微細化に向けた新手法、半導体チップの先進的なパッケージ技術などを複合的に検討している点だ。

この連載では、Logic Master Classで取り上げたトピックスの一部を紹介し、特に先端ロジック半導体のスケーリングに向けて乗り越えるべきトランジスタの設計上および物理上の制約を見ていくこととしたい。

トランジスタのスイッチング速度とばらつき

トランジスタはスイッチとして動作する。その性能を最高に高めるには、主としてドライブ電流の最大化とキャパシタンスおよび抵抗の低減を通じてスイッチング遅延を減らすことに力点が置かれる。

たとえばFinFETトランジスタでは、フィンの高さ、チャネルのゲート長、チャネルを通過する電子の移動度、スイッチングに用いるしきい値電圧、スイッチのオン/オフ状態を制御するゲート酸化膜の厚さなど、さまざまな物理的パラメータを調整して動作速度を速めている。電気抵抗については、高活性化されたドーパントをチャネル近くの領域に注入することで低抵抗化が図られる。

もう1つの重要な要因は、トランジスタ間のばらつきだ。特定の回路内で最も遅いトランジスタが性能のボトルネックになるので、ばらつきの幅を狭めるほど回路は高速化する。

FinFETの性能を妨げる要因:フィンの湾曲

次世代FinFETの設計におけるこの喫緊の課題について、より詳しく見ていきたいと思う。FinFETの構造は主に、チャネルとシャロートレンチアイソレーション、High-k/メタルゲート(HKMG)、そしてトランジスタ ソース/ドレイン抵抗の3モジュールに分けられる。

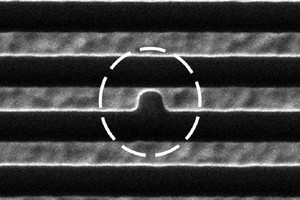

チャネルとシャロートレンチアイソレーションのモジュールについては、業界では数世代の技術ノードにわたってフィンの高さを増しフィン幅を狭めることで高速化を図ってきた。しかし、フィンをこれ以上高くして幅を狭めると、フィンの間に挟まれる素子分離用酸化膜の歪みによって製造プロセス中にフィンが湾曲しやすくなる。こうした湾曲は反力で歪みをもたらし、電子移動度を劣化させ、しきい値電圧に影響を及ぼして、トランジスタのばらつきを増大させることになる。こうしたフィンの湾曲を打ち消すには、新しいマテリアルズ エンジニアリングソリューションが求められる。

インタフェースとHKMGのスケーリングパリティ(ペース)を回復

HKMGモジュールは、トランジスタの心臓部にあたる。このメタルスタックはきわめて複雑な構造を持ち、インタフェース、High-k、メタルゲート層を含む少なくとも7層からなる。

インタフェース層とHigh-k層のスケーリングは、ゲート酸化膜の低減に重要で、それによりトランジスタのドライブ電流が増える。メタルゲートを調整することで、トランジスタの適正な機能が確保され、しきい値電圧が決まる。問題は、14nmノード以降インタフェース層とHigh-k層のスケーリングのペースが、トランジスタのドライブ電流を高める他の物理パラメータと同じペースではないことだ。そこで、インタフェースとHigh-kのスケーリングパリティ(ペース)を回復する新しいイノベーションが求められている。

プロセスノードの進展につれてコンタクトのボリュームが減少

3つ目の主要エレメントは、トランジスタ ソース/ドレイン抵抗モジュールである。新たなプロセス微細化が導入されるたびに、トランジスタのコンタクト部分の面積は技術ノードあたり約25%ずつ縮小し、抵抗の増加をもたらしている。これに寄与する主な要因としては、メタルコンタクトとシリコントランジスタ間のインタフェース抵抗、およびソース/ドレイン領域で発生する外部抵抗がある。

インタフェース抵抗とソース/ドレイン外部抵抗を緩和する上で求められるのは新しいマテリアル、そして複数のプロセスステップを協調して最適化することである。

Gate-All-Aroundトランジスタの基礎固め

上述のとおり、FinFETのフィンは、これ以上継続することができないほど高く狭くなっている。中でもフィン幅はプロセス微細化が進むにつれて制御が難しくなり、しきい値電圧のばらつきが増大してデバイス性能の低下につながっている。そこで業界では、gate-all-around(GAA)と呼ばれる新アーキテクチャへの移行を急いでいる。これはシリコンフィンを横向きにして、層状に重ね合わせたような形状をしている。

GAAトランジスタではフィンのばらつきを解決する新たな方法として、従来のリソグラフィとエッチングによる制御ではなく、エピタキシーと選択的除去が用いられる。これにより、フィン幅をきわめて精密に制御することが可能となる。パフォーマンスの面では、ばらつきが減少するとともにゲート長のスケーリングによってドライブ電流を10~15%増やすことができ、同時に消費電力も減る。

なおAMATでは自社の製品群を活用し、新しいマテリアルと組み合わせることで、こうした各種技術の実用化を進めている。

次回は、ロジック配線におけるRC遅延と消費電力の低減の課題を取り上げたいと思う。

この連載はApplied Materialsが発行している英文ブログをアプライド マテリアルズ ジャパンが翻訳したものを一部修正して掲載しております。

著者プロフィール

Mike ChudzikApplied Materials

ニューマーケット&アライアンス グループ R&Dアライアンス部門 テクノロジー担当マネージングディレクター

アジェイセント・エマージング分野(バイオMEMS、光学、パワーエレクトロニクス、新型メモリ、ニューロモーフィック インメモリ・コンピューティング、クライオロジック、量子など)の社外カスタマーとの協業プロジェクトにおいて、プロセスとインテグレーションを提供する責任を担うチームを率いる。現職以前は、AMATの半導体グループでクロスBUモジュールチームを統括していた。

最初に就職したIBMではDRAMとロジックデバイス用High-k絶縁膜を手掛け、同社で14年間にわたってプロセスからモジュール統合までさまざまな役割を担う。雑誌や会議向けに執筆ないし共同執筆した査読付き論文は60本を超え、エレクトロニクス材料、CMOSプロセシング、CMOSデバイス構造などで80件以上の特許を取得してIBM Master Inventorの称号を授与されている