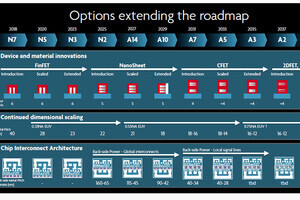

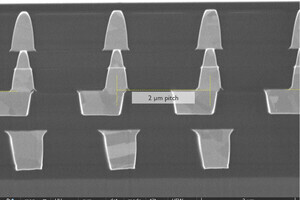

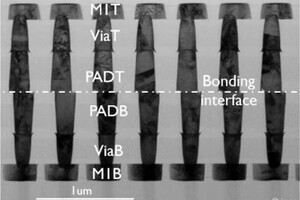

3D相互接続密度の継続的な増加により、内部インタフェースの保護が複雑になっている。半導体業界では、ロジック/メモリオンロジックタイプのスタッキングアプリケーションなどを対象に、各3D相互接続技術をより細分化した相互接続へと推し進めている。imecの研究者は最近、相互接続パッドピッチが2μmというダイ・ツー・ウェハのハイブリッドボンディングを実証した。ウェハ・ツー・ウェハのハイブリッドボンディングでは、わずか400nmの相互接続ピッチが達成され、ダイの表面で1mm2あたり100万を超えるCu相互接続に相当する[2][3]。

この進化のマイナス面は何だろうか? ボンディング中に内部I/O回路をESDから保護する保護回路に使用できるスペースがますます少なくなっている。最終的には、スペースがまったくなくなることが予想される。これにより、設計者はI/OインタフェースのESD保護回路をますます小さくせざるを得なくなる。ただし、これにより、スタッキングおよびアセンブリ中の内部I/OピンのESD耐性が低下する。そのため、ESDコミュニティは、ボンディング中のESDイベントの防止をますます推進し、最終的には可能な限り「内部」ESD保護回路の必要性を排除しようとしている。

ESD保護を少なくすることは、面積の消費量が少なくなるだけでなく、I/O回路のパフォーマンスにもメリットをもたらす。ESD保護回路は、寄生容量が追加されるため、保護対象の回路のパフォーマンスを直接低下させる可能性がある。したがって、ESD保護を追加することは、堅牢性とパフォーマンスのトレードオフになっている。

ESDの基礎的理解の強化

0V ESD保護に移行するには、ボンディング中にI/O内部ピンに発生する可能性のあるESDイベントに関する詳細な知識が必要である。「標準」モノリシックICの場合、ESD保護は比較的よく理解されている。しかし、2.5D/3Dテクノロジの内部I/Oインタフェースの場合、ESDイベントの影響はまだ明確ではない。

現在、2.5D/3DボンディングテクノロジにおけるESD保護対策の要件と目標レベルを規定した標準は存在しない。ESD関連の会議やワークショップで繰り返し報告されているように、テストに関する従来の想定は、高度なボンディングテクノロジや内部ピンには当てはまらないようである。測定結果から、ESDイベント後のESDパルスは、ピーク電流、パルス幅、立ち上がり時間に関して、たとえば標準CDMテストで想定されるものとは異なる動作をすることが示されている。

これには、より根本的な理解が必要である。ESDイベントが内部インタフェースにどれほど重大であるかを定量化することで、業界の目標レベルを設定するためのガイダンスが得られ、ファウンドリが予防策を講じるのに役立つ。さらに、ESDイベントと破壊メカニズムをモデル化することで、設計者はESD保護回路の設計を調整できる。

予防に投資し、過剰な設計を避け、カスタマイズされたアプローチを採用

imecでは、研究者チームが実験とモデリングを組み合わせて、ダイ・ツー・ウェハまたはウェハ・ツー・ウェハの積層中に静電放電によって生じる破壊メカニズムを解明している。彼らは、たとえばESD保護回路がない場合に内部I/Oバイスのゲート酸化物がどのように破壊されるかを調査している。さらに、ESD保護回路がある場合のESDパルスの形状も研究している。ESDパルスの形状に影響を与えるさまざまなパラメータを調べることで、ESD放電を完全に回避できない場合に、設計者が保護回路をより効率的にすることができる。最初の知見は、VLSIシンポジウム2024[4]で発表された。

これらの研究やその他の研究の結果は、例えばESD目標レベルに関する業界協議会[5]に報告されており、より広範なESDエコシステムに対するガイドラインや研究の方向性に反映させることができる。

参考資料

[2] 「imecは2μmのCu相互接続パッドピッチでダイ・ウェハハイブリッド接合を実証」、imecプレスリリース、2024年5月

[3] 「ウェハ・ツー・ウェハ・ハイブリッド接合:400nm相互接続ピッチの限界を押し上げる」、imec Website、2024年2月

[4] 「2.5D/3D先進ボンディング技術における0V ESD保護に向けて」SH Lin他、VLSI Symposium 2024 (Hawaii、2024年6月)

[5] ESD目標レベルに関する業界協議会、WP 2、パートII、改訂1.1、2023年

|

Shih-Hsiang (Shane) Lin

2018年に台湾の高雄にある国立高雄大学(NUK)で電気工学の学士号を取得したのち、2021年に台湾の台南にある国立成功大学(NCKU)で修士号を取得。さらに、2021年にはimecで1年間インターンとして働いた。2021年にブリュッセル自由大学(VUB)の電子情報学部(ETRO)博士課程に入学。同時に。ベルギーのimecの静電放電(ESD)チームに加わり、博士号取得を目指している。現在の研究テーマは、3次元(3D)技術におけるESDリスク調査である。 |

|

Marko Simicic

クロアチアのザグレブ大学で、2010年に電気工学、2012年に情報技術の理学士号、修士号を取得。2018年にベルギーのルーヴェン・カトリック大学(KU Leuven)工学部電気工学科で博士号を取得。2017年にベルギーのimecのESDチームに加わり、2022年から認定ESD制御プログラムマネージャーを務めている。国際ジャーナルや会議の議事録で35本以上の論文を執筆している。現在の研究分野はかなり幅広く、先進半導体や3D/2.5Dスタッキング技術におけるESDデバイスと回路の設計、新しいESDテスト、ESD制御プロセス評価などを行っている。 |

|

Nicolas Pantono

imecの主任技術者。2010年にベルギーのブリュッセル大学で電気工学の学士号、2012年に修士号を取得。2021年に、ベルギーのKU Leuvenの電気工学科で博士号を取得。さらに、2015年にはベルギーのSolvay Business Schoolで経営管理と財務の修士号を取得。2013年に、imecの3Dおよびシリコンフォトニクス部門に加わった。彼の研究は、モバイル、高性能コンピューティング、AI、自動車などのアプリケーション向けの2.5D/3D統合システムの電気および光相互接続に焦点を当てている。 |