imecの先端3D SoCにおける内部I/Oインタフェースの静電気放電(ESD)対策に関する論文が「Nature Reviews Electrical Engineering」に掲載された。今回、imecより翻訳の許可を得る形で、ベルギーimecで先端3D SoCのESD保護対策を研究している担当者らが、この論文で語っているダイまたはウェハ接合工程中における内部I/OインタフェースのESD保護に関するガイドラインを複数回に分ける形で紹介する。

2.5D/3D化で重要となるESDへの理解

2.5D/3D集積技術における相互接続密度の継続的なスケーリングにより、内部I/OインタフェースにESD保護回路を実装する余地がほとんどなくなった。このため、業界はダイ・ツー・ダイ(Die to Die)およびダイ・ツー・ウェハ(Die to Wafer)の接合ステップにおけるESD抑制にさらに多額の投資を強いられ、ESD保護回路の過剰設計を避ける必要に迫られている。

これを最も効率的に行うには、内部I/Oインタフェースで発生するESDイベントを、より根本的に理解する必要がある。この連載では、回路設計者とボンディングツールサプライヤ向けの実用的なガイドラインと研究の方向性について紹介したい。

モノリシックSoCにおけるESD保護戦略

ESDによる故障は、半導体業界にとって継続的な懸念事項である。ESDイベントは、製造および組み立て中、および製品の輸送中および使用中のどの時点でも電子製品に影響を及ぼす可能性がある。また、ESD放電は非常に短い時間枠で発生する。パルス幅は1ns未満から200ns、立ち上がり時間は200ps未満から10ns程度である。この短い時間枠で、0.1~10A程度の過剰電流がICおよびパッケージを流れ、金属配線の焼損やゲート酸化物の破壊を引き起こしてチップを損傷する可能性がある。

当然のことながら、業界は電子製品の安全確保に力を入れており、予防と保護の両方に重点を置いている。ESD イベントを可能な限り防止するために、ICの製造と組み立てはESD管理された施設で行われ、適切な材料が使用され、作業員と機器が適切に接地されている。予防策は、オンチップ保護回路を追加することで補完される。これらの回路は、チップを外部に接続するチップの入力および出力インタフェース(I/O)を保護する。ESDイベントがチップに発生すると、これらの回路は、電圧を安全なレベルに制限しながら、接地への安全で低抵抗の放電経路を確保する。

モノリシックなシステム・オン・チップ(SoC)の場合、ESD設計戦略は明確に定義されており、テクノロジロードマップに新しいテクノロジが登場するたびに進化している[1]。ESDイベントに対するチップの堅牢性を評価するために、半導体業界では、最も一般的なESDイベントを表す2つのESD制御標準、つまり人体モデル(HBM)と帯電デバイスモデル(CDM)を使用している。HBMは人体(および拡張して他の外部物体)からICへの放電を表すが、CDMはチップ自体が充電され、環境に放電するときに何が起こるかを捉える。業界では、さまざまな電子製品のESD目標レベルも設定している。今日、高性能コンピューティングアプリケーションで使用されるモノリシックSoCは、顧客の要求に応じて125Vまたは250V CDM に適合している。HBMの場合、仕様はI/Oピンの機能と顧客の要求に応じて100V~500Vの範囲である。

2.5D/3Dテクノロジーでは内部I/Oインタフェースが複雑さを増加させる

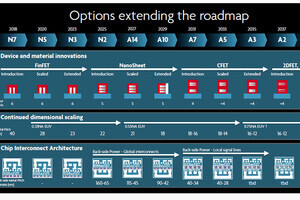

高度なコンピューティングシステムは、モノリシックなプレーナSoCから、2.5Dおよび3Dの相互接続テクノロジを使用することで異なるダイをスタックして相互接続するマルチダイ・ヘテロジニアス・システムへと進化している。

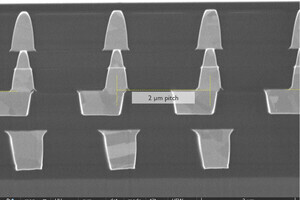

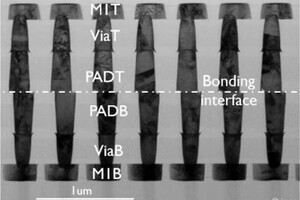

長年にわたってさまざまな3D相互接続テクノロジが開発され、さまざまな相互接続密度が提供され、さまざまなアプリケーションに使用されてきた。例えば2.5Dインターポーザテクノロジ(ダイが互いに隣接して配置され、(アクティブ)インターポーザを介して接続される)や、ダイ・ツー・ウェハまたはウェハ・ツー・ウェハのスタック用のマイクロバンプまたはハイブリッドボンディングアプローチなどがある。

ESDの観点から見ると、2.5Dおよび3Dテクノロジはさらなる複雑さをもたらす。パッケージ化された後も、3D スタックシステムは、システム全体を外部に接続するI/Oピンを備えている。パッケージ化された単一ダイの場合と同様に、これらの外部I/O回路は外部の物体や人間との間で静電放電される可能性があり、モノリシックIC用に定義された同等のESD制御規格は有効のままである。

しかし、それに加えて、3Dスタックシステムには、パッケージピンに接続せずにスタックの異なるダイ間を接続する内部I/O回路が含まれている。これらのインタフェースは、ダイまたはウェハのスタック中に発生するESDイベントに対してのみ脆弱である。たとえば、ダイのピックアップ、ダイの転送、ダイまたはウェハのボンディングプロセスなどである。したがって2.5/3Dテクノロジでは、スタックおよびアセンブリ中にESDイベントを可能な限り抑制することが重要である。ESDイベントが発生した場合、チップメーカーは、パフォーマンスに影響を与えることなく内部I/Oピンが十分に保護されていることを確認する必要がある。

参考資料

[1] 「薄いSi基板を使用した先進CMOS技術をESDから保護する方法」、imec Website、2024年2月

|

Shih-Hsiang (Shane) Lin

2018年に台湾の高雄にある国立高雄大学(NUK)で電気工学の学士号を取得したのち、2021年に台湾の台南にある国立成功大学(NCKU)で修士号を取得。さらに、2021年にはimecで1年間インターンとして働いた。2021年にブリュッセル自由大学(VUB)の電子情報学部(ETRO)博士課程に入学。同時に。ベルギーのimecの静電放電(ESD)チームに加わり、博士号取得を目指している。現在の研究テーマは、3次元(3D)技術におけるESDリスク調査である。 |

|

Marko Simicic

クロアチアのザグレブ大学で、2010年に電気工学、2012年に情報技術の理学士号、修士号を取得。2018年にベルギーのルーヴェン・カトリック大学(KU Leuven)工学部電気工学科で博士号を取得。2017年にベルギーのimecのESDチームに加わり、2022年から認定ESD制御プログラムマネージャーを務めている。国際ジャーナルや会議の議事録で35本以上の論文を執筆している。現在の研究分野はかなり幅広く、先進半導体や3D/2.5Dスタッキング技術におけるESDデバイスと回路の設計、新しいESDテスト、ESD制御プロセス評価などを行っている。 |

|

Nicolas Pantono

imecの主任技術者。2010年にベルギーのブリュッセル大学で電気工学の学士号、2012年に修士号を取得。2021年に、ベルギーのKU Leuvenの電気工学科で博士号を取得。さらに、2015年にはベルギーのSolvay Business Schoolで経営管理と財務の修士号を取得。2013年に、imecの3Dおよびシリコンフォトニクス部門に加わった。彼の研究は、モバイル、高性能コンピューティング、AI、自動車などのアプリケーション向けの2.5D/3D統合システムの電気および光相互接続に焦点を当てている。 |