Hot Chips 31においてXilinxはAIエンジンを持った「Versal」というFPGAを発表した。発表者はXilinxのシニアディレクタのSagheer Ahmad氏である。

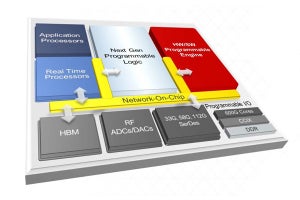

Ahmad氏は、Xilinxの製品はVirtexやKintexなどのFPGAとプロセサを含んだZynq-7000などのSoCがあるが、今回発表するVersalはAdaptive Compute Acceleration Platform (ACAP)という新しいカテゴリの第3のデバイスであるという。そして、Versalはこの新カテゴリのシリーズの最初のデバイスである。

-

Versalは従来のFPGAやSoCに続く第3カテゴリのAdaptive Compute Acceleration Platform(ACAP)という新デバイスにおける最初の製品である (出典:この連載のすべての図は、Hot Chips31でのXilinxのSagheer Ahmad氏の発表スライドのコピーである)

Versalの特徴は、従来のFPGAにAIエンジンを追加し、FPGAにも搭載されていたDSPをAI向けに改良した点である。また、AIエンジンは高いメモリバンド幅を必要とするのでチップ内のメモリアクセスネットワークを高速化している。

次の左側の図は、Versal VC1902チップ上の各機能ブロックのレイアウトを示す図であり、上辺にAIエンジンが置かれている。その下に横方向のチップ内ネットワークであるHNoCがある。もう1本のHNoCがDDRメモリコントローラとIOの上にあり、両方のHNoCの間を4本の縦方向のVNoCが接続して梯子のような構造のネットワークになっている。

そして、SerDesやDSP ColumnなどはVNoCと同方向の細長い領域に置かれている。

使用プロセスはTSMCの7FFで、370億トランジスタを集積している。メモリは855Mbit搭載し、AIエンジンは400コアを搭載している。

前述のように、Versalのオンチップネットワークは2本の水平の領域と4本の垂直の領域で構成されている。水平の領域には4本の物理チャネルがあり全体では>2Tbpsの双方向バンド幅をもっている。垂直の領域は2本の物理チャネルを持ち、4つの領域の合計のバンド幅は、水平の領域と同じ>2Tbpsである。

そしてNoCの概念的な構造が示されているが、左側から入力が入り、クリーム色の丸で書かれているスイッチで経路を選択するメッシュ構造になっている。出力は右側から出力される。

プログラマブルロジック(PL)やその他のブロックは、このオンチップネットワークで接続される。

メモリサブシステムは単一で、64bit 4本、あるいは32bit 8本の入出力として使える。DDR4メモリは最大3200MHz、LPDDR4メモリは最大4266MHzで使用でき、また、このメモリポートはMIPIなどの並列IOポートとしても使用可能である。

Versalは、プロセサとしてはCortex-A72を2コアとリアルタイムOS用のCortex-R5を2コア搭載している。2つのCortex-R5はロックステップ動作が行なえ、ASIL-Cの安全性を持つシステムを作ることが可能である。

Versalの再構成可能ロジックゲートの部分は、従来よりも4倍大きなCLBとなり、32LUTとなった。次の図では32個のLUTはクロスバで接続されている感じの絵が描かれている。また、FFも従来の16個から64個に増加している。そしてVersalチップ全体では、90万個のLUTと180万個のFFを持っている。メモリは、URAMとBRAMの合計で、158Mbitを集積している。

(次回は10月2日に掲載します)