本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

論理回路のLogical Effort

CMOS回路がスイッチする遅延時間は、ゲートを構成するトランジスタを通して流れる電流で負荷となる容量を電源電圧Vddの1/2の電圧まで充放電する時間で決まる。充電する負荷容量は、次段のゲートの入力容量と配線の寄生容量が主な要素である。

ゲートを構成するトランジスタを全て2倍に大きくすると充放電する電流も2倍となる。しかし、次段のゲートのトランジスタも2倍にすると入力容量も2倍となり、遅延時間の改善効果は2倍より小さい。ゲートを構成するトランジスタをどんどん大きくしていくと、ついには配線の寄生容量はゲートの入力容量に比べて無視できる程度に小さくなり、これがゲート遅延時間の下限となる。この下限の遅延時間はトランジスタのゲート入力容量とドレイン電流の比で決まる。ITRS2004では2入力NANDゲートに同じゲート3個を負荷として接続した場合の遅延時間が示されており、90nmテクノロジでは約24ps、2007年の65nmテクノロジでは約16psとなっている。

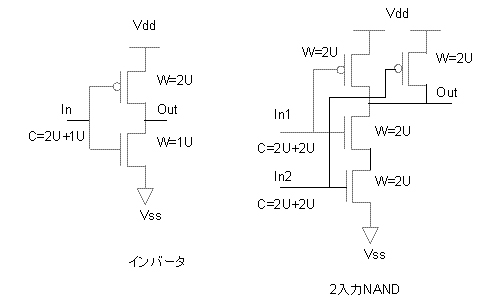

この図はインバータと2入力NANDのトランジスタ回路を示している。インバータはP-TrがオンになるとOutをVdd方向に充電し、N-TrがオンになるとOutをVss(グランド)に放電する。一般にはLow(Vss)→High(Vdd)とHigh→Lowの両方向のスイッチの遅延が同程度になることが望ましく、P-Trの大きさ(ゲート幅 W)をN-Trの2倍程度に取る。そのため、ここではN-Trのサイズは1 Unit、P-Trのサイズは2 Unitとした。

一方、2入力NANDはN-Trが2個直列に接続されている。抵抗を直列に接続した場合と同様に、トランジスタも2個直列に接続すると1個の場合に比べて流せる電流はほぼ1/2になる。一方、P-Trは2個並列になっているが、in1、in2の一方だけがLowになった場合は、1個だけがオンする。このため、2入力NAND回路では、(1入力がスイッチした場合の)Low→High、High→Lowの遅延を同程度にするためにN-TrとP-Trのサイズはともに2Uが適当である。この図には無いが、3入力NANDではP-Trが3個並列になり、N-Trは3個直列になるので、N-TrはP-Trの1.5倍の3Uサイズが適当である。

このように、同じ放電電流を流そうとすると、インバータより2入力NAND、2入力NANDより3入力NANDではN-Trを大きくする必要がある。この関係を総合して表わす考え方としてLogical Effortという理論がある。同じサイズのN-TrとP-Trでは流せる電流が2対1の場合、インバータでは2UのP-Trと1UのN-Trが用いられる。入力容量はP-TrでもN-Trでもトランジスタのチャネル幅Wが同じであると、ほぼ同じである。従って、インバータの入力容量Cは3 Unit分である。2入力NANDではN-Trが2個直列になるので2倍のサイズが必要であり、各入力は1個のN-Trと1個のP-Trに接続されるので、入力容量Cは4 Unit分となる。

以上の説明では、充放電電流を一定にするようトランジスタサイズを選んだが、逆にインバータと入力容量を同じにするためには、2入力NANDを構成する全トランジスタの単位サイズ Uを3/4に縮小する必要があり、充放電電流も3/4となる。つまり、同一入力容量とした場合、同じ負荷容量をつけた2入力NAND回路の遅延時間は、インバータの4/3倍となる。この4/3倍が2つの入力のNANDを取るという論理動作に必要な努力(Logical Effort)である。同様に、3入力NANDの入力容量は5 Unit分であり、Logical Effortは5/3となる。

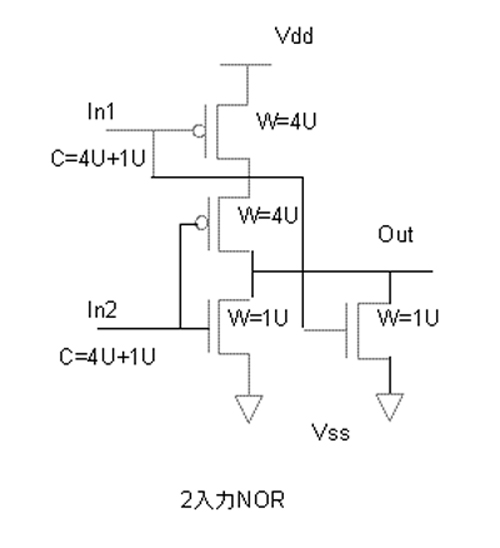

一方、次の図に示すように2入力NOR回路ではP-Trが直列になり、N-Trが並列に接続される。電流駆動能力の小さいP-Trが直列になるので、直列にならないN-Trと同じ電流を流すためにはP-Trのサイズは4Uにする必要がある。

このため2入力NOR回路の入力容量Cは5 Unit分となり、Logical Effortは3入力NANDと同じ5/3となる。NANDとNORは相補的な関係にある論理演算であるが、一般的なCMOSではP-TrとN-Trの電流駆動能力がアンバランスであることからNOR回路の方が大きなLogical Effortとなる。このため、実際の論理設計では、信号の極性を工夫してNANDを多く使うように回路を設計することが多い。

なお、以上の説明では、同じサイズのN-TrはP-Trの2倍の電流が流せると想定してトランジスタサイズを決め、Logical Effortを計算したが、実際の半導体プロセスではこのN-TrとP-Trの電流比は厳密に2対1ではなく、多少異なっている。特に、最近の歪シリコン技術を用いるとP-Trの電流改善の方が大きく電流比は1対1に近づく。従って、回路を設計する場合には、実際に使用する半導体プロセスのP-Tr、N-Trの電流比に合わせてトランジスタサイズを決め、Logical Effortを求めるのが良い。