imecでは、CFET実現に向けて困難なn-MOSトランジスタとp-MOSトランジスタ対を垂直スタッキングを可能にするために、モノリシックとシーケンシャルの2つの集積方式が検討されている。

モノリシックCFETのプロセスフローは、下部チャネルのエピタキシャル成長から始まり、中間犠牲層の堆積が続き、次に上部チャネルのエピタキシャル成長が続く。堀口氏は「これはCFETを構築する最も簡単な方法のように見えるが、処理フローはかなり複雑である。たとえば、いくつもの層の積み上げによって非常に高いアスペクト比の垂直構造が生じ、フィン、ゲート、スペーサー、およびソース/ドレインコンタクトをパターニングする際にさまざまな課題に直面する」とプロセスの複雑さを強調している。

別の方法として、CFETは、いくつかのブロックからなる一連のプロセスフローを使用して作製することもできる。まず、最下層のデバイスをコンタクト工程まで終える。次に、ウェハ・ツー・ウェハ・ボンディング技術を使用して、ウェハ転写によってこの層の上にブランケット半導体層を作製する。最後に最上層のデバイスを集積し、トップゲートとボトムゲートを接続する。

Ryckaert氏は「集積の観点から見ると、このフローはモノリシックフローよりも簡単である。最下層デバイスと最上層デバイスの両方を従来通りの『2次元』の方法で別々に処理できるからだ。さらに、n型デバイスとp型デバイスそれぞれに適した異なるチャネル材料を集積できることがこのフローのメリットである」と述べている。

これら2種類のフローには、それぞれ長所と短所がある。imecは、モジュールと集積ステップを開発し、電力・性能・面積・コスト(Power/performance/Area/Cost:PPAC)の評価と各プロセスフローの複雑さを定量化し、2つの方式を比較しようとしている。

PPACベンチマーク:最適化されたシーケンシャルCFETは、モノリシックCFETの有効な代替手段

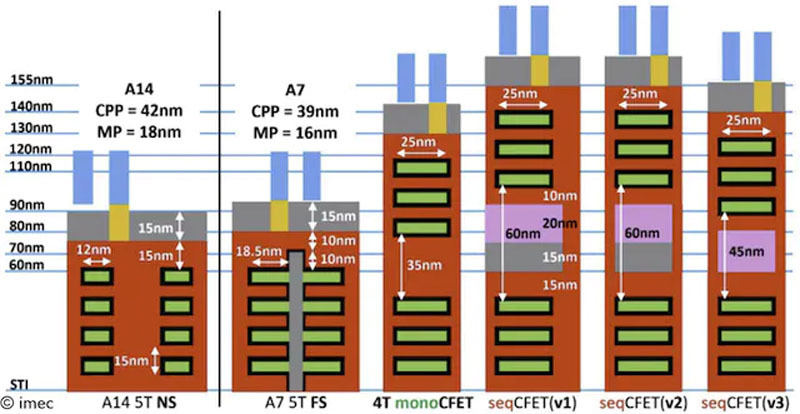

P. Schuddinck氏らによるVLSIシンポジウム2022の報告で、4T標準セル設計におけるモノリシックCFETとシーケンシャルCFETのPPAC評価が提示された。

Ryckaert氏は、「このベンチマークにより、モノリシックプロセスフローを使用して製造されたCFETは、実効キャパシタンスの増加に悩まされているシーケンシャルCFETよりも消費面積が少なく性能が優れていることが示された。ただし、私たちは、3つの最適化を適用することにより、シーケンシャルCFETの性能をモノリシックCFETの性能と同等にすることができることを明らかにしている。その3つの最適化とは、(1)自己整合ゲートマージ(図4のv2)、(2)ゲートキャップの省略(同v3)、および(3)HOTと呼ばれるハイブリッド・オリエンテーション・テクノロジ(HOT)の使用である。

-

図4 ナノシート(NS)、フォークシート(FS)、およびCFET(モノリシックおよびシーケンシャル)それぞれのゲート断面模式図。基本的なシーケンシャルCFET(v1)は、モノリシックCFETより幅が広く高さが高くなっている。最適化されたフロー(セルフアラインゲートマージ(v2)およびゲートキャップなし(v3)を含む)により、シーケンシャルCFETは面積消費の点でモノリシックCFETに近づいている(2022 VLSI Symposiumで発表)

HOTでは、プロセスフローコストを増加させることなく、トップデバイスとボトムデバイスの結晶方位と移動度を増すための結晶ひずみを個別に最適化できる。たとえば、n-on-p構成では、上部に<100>Siウェハを使用することにより、上部nMOSデバイスに最高の電子移動度を提供できる。一方、底面については、<110>Siウェハを採用することでpMOSトランジスタホール移動度向上の恩恵を受ける。

Ryckaert氏は、「モノリシックCFETが依然として好ましい選択肢であるが、シーケンシャルプロセスフローの特長は、ウェハの結晶方位の違いを利用できることである。これらの最適化により、私たちのベンチマークでは、シーケンシャルCFETフローが、将来の4T設計のためのより複雑なモノリシックCFETの有効な代替手段になり得ることを示している」とシーケンシャルCFETのメリットを強調している。

モジュールおよび集積ステップの段階的な改善

近年、imecはモノリシックおよびシーケンシャルCFETのモジュールおよび集積ステップの改善について順次報告してきた。たとえば、VLSI Symposium 2020で、imecはモジュールの改善について報告し、モジュールステップを最適化することによって実現したモノリシック集積のCFETアーキテクチャを初めて実証した。

シーケンシャルCFETについても、段階的な改善が報告されている。最下層と最上層のデバイスは、従来の「2次元」の方法で別々に処理できるが、ウェハ転写には課題がある。

たとえば、最下層のデバイスへの悪影響を回避するために、レイヤ転写と最上層のデバイス処理の両方に熱バジェットの制約(約500℃以下まで)が伴う。これは、通常 900℃程度の熱ステップを必要とする最上層デバイスのゲートスタックの信頼性に対する懸念事項である。以前imecは、特にpMOSトップデバイスの低温水素プラズマ処理を含む、良好なゲートスタック信頼性を維持するための新しいアプローチを実証した。また、imecは、ボイドのない薄い接合酸化膜プロセスを開発することにより、誘電体と誘電体のウェハ接合ステップの進歩を報告した。

(次回に続く)

|

堀口直人

imecのロジックCMOSスケーリングプログラムディレクター。1992年に富士通研究所入社。1999年まで富士通研究所やカリフォルニア大学サンタバーバラ校にて半導体ナノ構造を用いたデバイス開発に従事。2000年から2006年まで、富士通でインテグレーションエンジニアとして90-45nm CMOS技術の開発に携わった後、2006年よりimec勤務。以降、世界中の産業パートナー、大学、研究機関とともに高度なCMOSデバイスの研究開発に携わっている。現在の注力事項はCMOSデバイスの1nmテクノロジノード超のスケーリング |

|

Julien Ryckaert

imecのロジック微細化担当副社長。2000年にベルギーのブリュッセル大学(ULB)で電気工学の修士号を取得、2007年にはブリュッセル自由大学(VUB)で博士号を取得。2000年にミクスドシグナル設計者としてimecに入社、RFトランシーバ、超低電力回路技術、およびアナログ/デジタルコンバータの設計に従事。2010年に3D ICの設計を担当するプロセス技術部門に異動。2013年以降、先進CMOSテクノロジノード向けの設計技術同時最適化(DTCO)プラットフォームを統括。2018年に、3nmテクノロジノードを超えるスケーリングとCMOSの3D スケーリング拡張に焦点を当てたプログラムディレクターに就任 |