次世代デバイスメモリの本命「HBM」

GDDRメモリは、GPUと1対1に短い配線で接続することでデータ転送速度を改善してきたのであるが、消費電力の制約もあり、今後、大きな性能向上は望めない状況になっている。

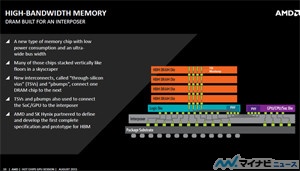

このため、注目を集めているのが、「High Bandwidth Memory(HBM)」のいう技術である。4枚(あるいは8枚)のDRAMメモリチップを積層し、メモリチップを貫通するThrough Silicon Via(TSV)という技術を使って重ねたメモリチップから配線を引き出す。チップの周囲からパッケージまで配線する従来の技術と比べると、チップを貫通して面から配線を引きだせる点と、TSVの接続が微細であることから、従来のワイヤボンド接続に比べて多数の配線を引き出すことができる。

そして、LSIの配線を作るのと同様の技術を使って作られ、プリント基板と比べて微細な配線ができるシリコンインタポーザという配線基板を使ってTSVで引き出された微細な配線を接続する。

|

|

図3-54 4枚のメモリチップと1枚のロジックチップをTSVで積層するHBMメモリとシリコンインタポーザによるGPUとの接続の構造を示す図 (出典:Hot Chips 27に於けるAMDの発表スライド) |

2015年7月にAMDはHBMを使う「Radeon R9 Fury」というGPUを発売した。HBMの信号ピンのデータ伝送速度は1Gbit/sと遅いが、信号ピンが多いので、GDDR5よりも高いメモリバンド幅が得られる。Radeon R9 FuryではHBM 1個あたり1024Gbit/s(128GB/s)のメモリバンド幅を持ち、4個のHBMの合計で512GB/sを実現している。従来の最上位製品はGDDR5 DRAMを16個使用して320GB/sであり、HBMの採用で1.6倍のメモリバンド幅となっている。

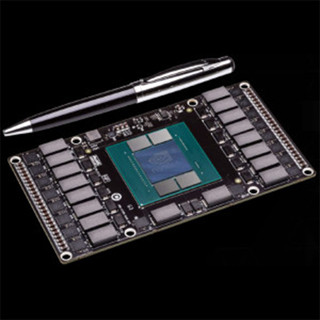

AMDのFury GPUの実物(キャップは除かれて内部が見える状態にした)は次の図3-55のようになっている。

|

|

図3-55 AMDのRadeon R9 Fury GPU。中央のAMDマークのチップがGPUで、その両側にある4個の黒いチップがHBM。これらのチップを囲み、光を反射している鏡面の部分がシリコンインタポーザが見えている部分である (出典:Hot Chips 27でのAMDの発表資料) |

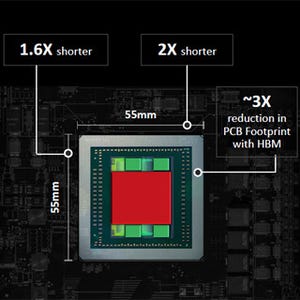

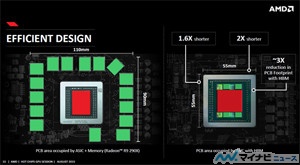

また、GDDR5メモリはプリント板に搭載され、大きな面積を必要としていたが、メモリがHBMになることにより、プリント板の必要面積がおおよそ1/3と小型化されている。

|

|

図3-56 従来のGDDR5 DRAMを搭載した基板とHBMを使うFury GPUとのプリント基板面積の比較。面積は約1/3と小型化できる (出典:Hot Chips 27におけるAMDの発表スライド) |

なお、NVIDIAも2016年より生産を開始したPascal GPUにて第2世代のHBM(HBM2)を採用することを発表している。HBM2では信号ピンのデータ伝送速度が2倍に上がり、1個で256GB/sのメモリバンド幅が実現できるようになる。

HBMの規格ではDRAMアレイにECCビットを追加し、ECCを行うという機能がオプションとして設けられている。当初は、ECCビットの生成、チェック、訂正の機能が内蔵されるという話もあったが、ISSCC2016で発表されたSamsung、SK hynixのHBM2では、ECC用に必要となるメモリは内蔵するが、ECCビットの処理機能は内蔵せず、GPU側に持たせる構成となっている。