技術研究組合 最先端半導体技術センター(LSTC)は4月13日、新エネルギー・産業技術総合開発機構(NEDO)が推進する「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発(委託)」において、LSTCが提案していた「光電融合を加速する半導体パッケージング技術開発と先端後工程拠点形成」が採択されたことを発表した。

同事業は、生成AIやHPCの普及に伴って急増するデータ通信量と消費電力の課題解決を目的に、チップレット間通信を従来の電気配線から光配線へと進化させる次世代パッケージング技術の確立を目指す取り組みである。

電気配線の限界を超える「光電融合パッケージング」

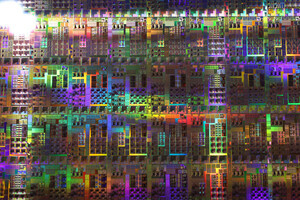

AI社会の進展により、半導体にはこれまで以上の演算性能とデータ転送能力が求められている。一方、従来の電気配線による信号伝送は、帯域や消費電力の面で限界が顕在化しつつある。LSTCが取り組むのが、こうした制約を根本から見直す光電融合パッケージング技術となる。

同事業では、電子回路(EIC)と光集積回路(PIC)を組み合わせた「光エンジン」を、有機インターポーザ上に6μm以下の狭ピッチで高精度にハイブリッド接合する技術「狭ピッチハイブリッド接合」を開発する。これにより、10Tbps/mm級の高帯域伝送と、伝送量当たり40%以上の消費電力削減を実現することを目標に掲げている。

光RDLインターポーザとCPO技術を中核に

技術的な中核となるのが、「光RDL(Redistribution Layer)インターポーザ技術」で、ポリマー光導波路やマイクロミラー、高効率な光結合素子を高度に集積し、電気配線では到達が難しい帯域密度を光配線で補完する。

この光RDLインターポーザと、EIC/PICを積層した光エンジンを組み合わせた「集積化Co‑Packaged Optics(CPO)」技術を活用することで、CPUやGPU、AIアクセラレータなどのxPUやHBMを含むチップレット構成においてて、パッケージ内光配線の本格的な適用を進め、データ転送密度の向上と消費電力の削減の両立を目指すこととなる。

世界初の300mm角対応・先端後工程オープン拠点を千歳科学技術大に整備

技術開発と並んで重要な柱となるのが、社会実装の要となる先端後工程拠点の形成で、LSTCでは組合員の一者である公立千歳科学技術大学内に、300mm角パネル対応の装置群を備えた世界初となる先端後工程オープンイノベーション拠点を整備する計画としている。

同拠点は、半導体パッケージングにおける量産スケールを見据えた検証と、産学官連携による共同開発のハブとして位置付けられ、先端半導体パッケージングの技術開発を社会実装へとつなげる役割も担うことが予定されている。

imecとの国際連携で開発力を強化

同事業は、LSTCの組合員である東北大学、産業技術総合研究所、北海道大学、公立千歳科学技術大学、横浜国立大学、Rapidusが中心となって進められるが、再委託先としてimecおよびimec Japanとも国際連携が進められるとのことで、国内外の研究機関・企業が関与する体制を通じて、光電融合パッケージングに関する国際的な知見の集約と標準化を目指すこととなる。

LSTCは今回の取り組みを通じて、次世代AI・HPCインフラの性能向上に貢献するとともに、国内サプライチェーンの強化と日本の半導体産業の国際競争力向上につなげたい考えだ。

半導体の高性能化を後工程が担う時代へ

半導体の高性能化は、これまでプロセスの微細化を核とした前工程が主に担っていた。しかし、微細化が物理限界に近づきつつある現在、プロセスノードの進化による性能向上は継続しているものの、その成長速度は鈍化している。その一方で、AI活用などの分野から求められる性能向上の度合いは高まる一方であり、チップレットを活用する形での大規模集積の実現と、それに伴って増加する消費電力の抑制が後工程ならびにパッケージング技術に求められるようになっている。

LSTCが同事業で掲げた光電融合パッケージングと先端後工程拠点の整備は、こうした流れを象徴する試みと言える。AI時代の半導体は、単一チップの性能競争から、実装を含めたシステム全体の最適化へと重心を移しつつあるといえる。そうした状況の中にあって、日本で生み出されるパッケージング技術がどこまで存在感を示せるのか、同事業の動きが試金石となりそうだ。