キオクシアがIEDM 2025で積層可能な酸化物半導体チャネルトランジスタ技術を報告

キオクシアは12月12日、高密度・低消費電力3D DRAMの実用化に向けた基盤技術として高積層可能な酸化物半導体チャネルトランジスタ技術を開発したことを発表した。

同成果の詳細は、12月6日~10日にかけて米国サンフランシスコで開催されたIEEEの電子素子に関する国際会議「International Electron Devices Meeting(IEDM:国際電子デバイス会議)2025」にて、現地時間の12月10日に発表された。

3D DRAM実現に向けた課題を酸化物半導体で解決

AI時代に求められる大量のデータ処理のために、従来以上に大容量かつ低消費電力のDRAMの実現が求められている。しかし、従来の平面構成のDRAM技術はメモリセルの微細化が物理限界に近づいており、さらなる大容量化に向けてメモリセルを3次元的に積層する3D DRAMの実用化に向けた研究が各所で進められている。このメモリセルの積層においては、従来DRAMと同様の単結晶シリコンをトランジスタのチャネル材料に使用すると、製造コストが高くなり、かつメモリ容量に比例してメモリセルをリフレッシュするための電力も増加するという課題があった。

そこで同社では、そうした課題解決に向けて2024年開催のIEDMにて酸化物半導体の縦型トランジスタを用いたOCTRAM(Oxide-Semiconductor Channel Transistor DRAM)技術を発表。今回のIEDMでは、OCTRAMの3次元化に向けて、高積層可能な酸化物半導体チャネルトランジスタ技術を開発し、トランジスタを8層積層し動作することを確認したことを報告したという。

積層化におけるコストと電力の課題を解決

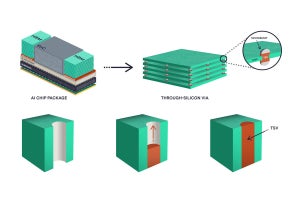

具体的には、一般的なシリコン酸化膜とシリコン窒化膜を積層膜として用い、シリコン窒化膜領域を酸化物半導体(InGaZnO)にリプレースすることで、縦方向に一括で横型トランジスタを形成するプロセスを採用するとともに、縦方向のピッチのスケーリングを可能とする3次元メモリセル構造を導入したとする。

これらの製造プロセスと構造によって、メモリセルの積層化におけるコストの課題を克服することが期待できるようになるとするほか、酸化物半導体の低いオフ電流という特徴により、リフレッシュ電力を抑制することも期待できるようになるという。

実際に同社ではリプレースで形成した酸化物半導体の横型トランジスタの高いオン電流(>30μA)と低オフ電流(<1aA、 10-18A)を実証したとするほか、横型トランジスタを8層一括で形成し、動作に成功したとしている。

なお、同社では今回開発した技術を活用することで、AIサーバーやIoT製品など幅広いアプリケーションにおいて低消費電力化を実現する可能性があると説明しており、今後も引き続き、同技術を用いた3D DRAMの実用化に向けた研究開発を進めていくとコメントしている。