スイスのSTMicroelectronics(STマイクロエレクトロニクス)は、次世代パネルレベル・パッケージング(PLP)技術の開発を、フランス・ツール工場で2026年第3四半期から新たに稼働する予定のパイロットラインで進めることを明らかにした。

PLP技術は、製造効率を高めてコストを削減する、先進的な自動化チップ・パッケージング/テスト・プロセス技術。次世代電子デバイスの小型化や高性能化、コスト効率の向上を実現する重要な要素だという。

同技術は、円形ウェハに代わり大型の長方形を使用する大面積キャリアであるため、製造スループットが高く、量産効率が高いとアピール。STは、マレーシアで稼働中の第1世代PLPラインとグローバルな技術研究開発ネットワークをベースに、次世代PLP技術の開発を進め、車載/産業/コンシューマ機器向けの幅広い製品へと適用拡大するとしている。

ツール工場の新しいPLPパイロット・ラインの開発には、6,000万ドル以上の設備投資を行っており、STの製造体制を再構築する全社的なプログラムの一部として割り当てたものだという。また、CERTEM研究開発センターなど、地域の研究開発エコシステムとのさらなる相乗効果も期待されているとのこと。

同プログラムでは先進的な製造インフラに注力し、「フランスとイタリアにおける複数の製造拠点に再定義されたミッションをもたらし、長期的な成功を支援する」としている。

PLPに関する技術情報

半導体業界では、シリコンチップを外部回路に接続するためウェハ・レベル・パッケージング(WLP)とフリップチップ技術を長らく利用してきたが、半導体の小型化と集積化が進むにつれ、これらの手法は拡張性とコスト効率の面で限界に達しているとされる。先端パッケージングでは既存のものや開発中のものを含めて各種のアプローチがあり、PLP技術はそのひとつと位置づけられている。

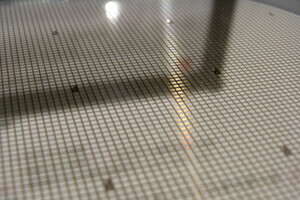

PLPでは、多数のICを個別の円形ウェハではなく、ひとつの大きな長方形の基板パネル上にパッケージングする。これにより、より多くのICを同時に処理できるため、コストの削減とスループットの向上が可能になるという。

STは2020年以来、PLP-DCI(ダイレクト銅配線)の採用だけでなく、同技術の開発を積極的に行ってきた。同社の研究開発チームによる試作開発と拡張した結果、最先端のPLP-DCIプロセスとして結実。現在、700×700mmという“非常に大型のパネル”を使いる高度な自動化ラインで、1日あたり500万個以上の量産を実現している。

STのPLP技術では、チップをワイヤ接続する従来方式に代わって、封止支持体を用いるダイレクト銅配線(DCI)に注力。DCIは導電性の優れた銅線を使い、ICとパネル基板の電極を電気接続するプロセスで、はんだバンプを使った従来の手法と比べて、高い性能が得られるとしている。

ワイヤボンディングを使わず直接接続するDCI技術は、電力損失の削減(抵抗やインダクタンスなど)や、放熱性の向上、小型化によって新製品の開発に寄与し、全体的な電力密度の改善につながるとのこと。また、SiP(システム・イン・パッケージ)など先進的なパッケージ内での複数チップの集積も可能だという。