SynopsysがTSMC A16の設計フローで協業

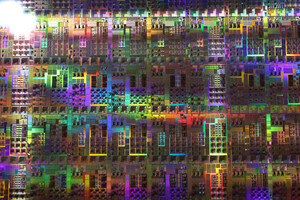

Synopsysは4月23日(米国時間)、TSMCと先端プロセスとなる「TSMC A16(1.6nmプロセス)」ならびに先端パッケージング技術向けEDA/IPソリューションの協業を発表した。

これにより、A16プロセスならびにN2Pプロセス上でのデジタル/アナログ設計フローにより、デザイン性能が向上し、アナログ・デザインのプロセス移行が加速されるとSynopsysでは説明している。また、この設計フローはSynopsys.aiとTSMCのA14(1.4nm)プロセス向けEDAフロー開発の早期段階の成果を活用したものとなるともしており、A14プロセスに向けたEDAフローの開発も協力して進められていることを強調している。

この取り組みにより、設計者はTSMC A16プロセスにおける認証済みの背面配線機能を活用して、より最適な電力分配や性能向上を実現できるようになるほか、パターンベースのピンアクセス手法もA16ならびにN2P向けに強化されており、より省面積で競争力のあるデザインを実現できるようになるという。加えて、SynopsysのFusion Compilerは、周波数最適化(Fmax)エンジンとインテリジェントなリーガライゼーション・テクノロジの強化によって性能が向上しており、N2P向けデザインのさらなる最適化を実現できるようになるともしている。

3nmプロセスでも協業を深化

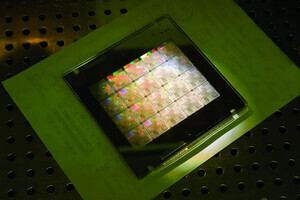

さらに、両社は既存のN3P設計ソリューションをベースに、新たに発表されたTSMC N3C技術のツール認証にも取り組んでいることを明らかにしたほか、TSMC認証済みのSynopsys 3DIC Compilerは、ダイを高密度に3D積層させた半導体設計を加速するため、3Dblox、ならびに5.5倍のレチクル・インターポーザ・サイズを持つCoWoS技術をサポートするともしている。

さらにシノプシスは、TSMC社の最先端プロセスに対応した完全かつシリコン実証済みのIPソリューションを提供しており、設計者が次世代設計に必要な機能をチップに迅速に統合し、最少の消費電力で最高の性能を実現できるよう支援している。

先端パッケージングの高性能化でも協力

このほか、両社は3DIC CompilerのCoWoSテクノロジー対応を通じて、5.5倍のレチクル・インターポーザ・サイズのサポートにより、ウェハ・オン・ウェハおよびチップ・オン・ウェハの高度なパッケージングを使用して、次世代HPCおよびAIチップで要求されるコンピューティング性能要件を満たすことが可能となるとする。加えて、2.5Dおよび3Dマルチダイ設計へのシームレスな移行を実現するために、3DIC Compilerは3Dbloxをサポートしており、分析ベースでの実現可能性の検討、プロトタイピング、フロアプランニングのための単一の環境が提供されることとなり、これにより、高密度な内部配線を実行する高効率な自動配線が可能となり、生産性の向上を可能とする。ちなみに3DIC Compilerには、電力/熱/信号整合性の解析を実行するAnsysのシミュレーション・テクノロジを用いたマルチ・フィジックス・サインオフ解析ソリューションが統合されているという。

なお、SynopsysはTSMCのN2/N2Pプロセス向けに高性能かつ省電力を実現するインタフェースIPおよびファウンデーションIPソリューションを提供しており、それらの中には、1.6T Ethernet、PCIe 7.0、UCIe、HBM4、USB4、DDR5、LPDDR6/5X/5、MIPIなどの主要な標準規格に準拠したものも多く、Synopsysでは、PCIeおよびEthernet IPに基づいた標準規格準拠のUALinkおよびUltra Ethernet IPもポートフォリオに加えたことも明らかにしている。