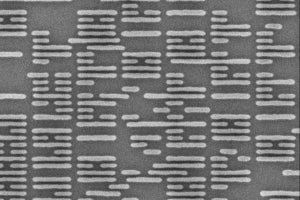

imecが2月下旬に米サンノゼで開催された先進リソグラフィとパターニングに関する国際会議「SPIE Advanced Lithography + Patterning」にて、高NA(NA=0.55)EUVリソグラフィを用いてパターン形成した20nmピッチの金属配線構造の電気テスト(eテスト)結果を発表した。

サーペンタイン型(一本の配線が蛇行した構造)とフォーク・フォーク型(2つのフォークが向き合ってお互いのスロットに入り込んだような構造)の両方の金属配線構造の測定では、良好な電気的歩留まりを示しており、確率的欠陥の数が少ないことを確認したという。eテストの結果は、高NA EUV露光装置とその周辺のエコシステムが、微細な寸法で線/スペースをパターニングできる能力を裏付けるものだとimecは主張している。

20nmピッチ配線で良好な歩留まりを確認

imecは2024年8月に、単一の高NA EUV露光でパターニングされたロジックとDRAMの良好なパターン結果を公表していた。

この成果を踏まえimecは新たなステップとして今回、金属酸化物(MOR)ネガトーンレジストを用いた単一の高NA EUVパターン化後に得られた20nmピッチの金属配線構造が、90%を超える歩留まりを示したことを発表した。このパフォーマンスは、確率的欠陥に関する情報を明らかにするように設計された、蛇行構造とフォーク・フォーク構造の2つの異なるテスト構造から得られた。

imecの研究開発担当シニアバイスプレジデントであるSteven Scheer氏は、「これらの結果は、高度なレジストと下地、フォトマスク、計測技術、イメージング、光近接効果補正(OPC)、統合パターン形成およびエッチング技術など、高NA EUVリソグラフィとその周辺エコシステムの機能の初期検証の成果を表している。今後も歩留まり向上を推進し、これらの技術を製造パートナーに移転するためのプロセスについて、パターン形成エコシステムと引き続き協力していくつもりである」と述べている。

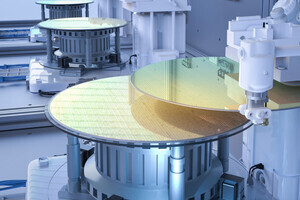

imecとASMLが共同運営しているimec/ASML High NA Labのエコシステムには、半導体、材料/レジスト、マスク、計測などのメーカーが含まれ、2nm未満ノードの半導体製造に向けた高NA EUVリソグラフィの開発と最適化に取り組んでいる。

imecの高度パターニング部門ディレクターのPhilippe Leray氏は「今回のeテストの結果は、今後の方向性も示している。電子ビーム検査と組み合わせると、メタライズされた蛇行構造とフォーク・フォーク構造の導電率測定から、歩留まり低下につながる確率的欠陥(破損によるオープン不良とブリッジによるショート不良)に関する情報が得られる。これらの洞察は、確率的欠陥を軽減する戦略の開発において、エコシステムパートナーをサポートする。現在、確率的欠陥への影響を最小限に抑えながら、EUV露光線量の削減という観点からレジスト性能を最適化することに重点を置いて、レジスト コミュニティと緊密に連携して取り組んでいる」と述べている。

なお、これらの結果は、SPIEにおける2つの論文で発表された。