ベルギーの独立系先端半導体・デジタル技術研究機関であるimecは11月5日、東京都内で創立40周年記念年次研究成果発表会「imec Technology Forum Japan 2024(ITF Japan 2024)」を開催した。

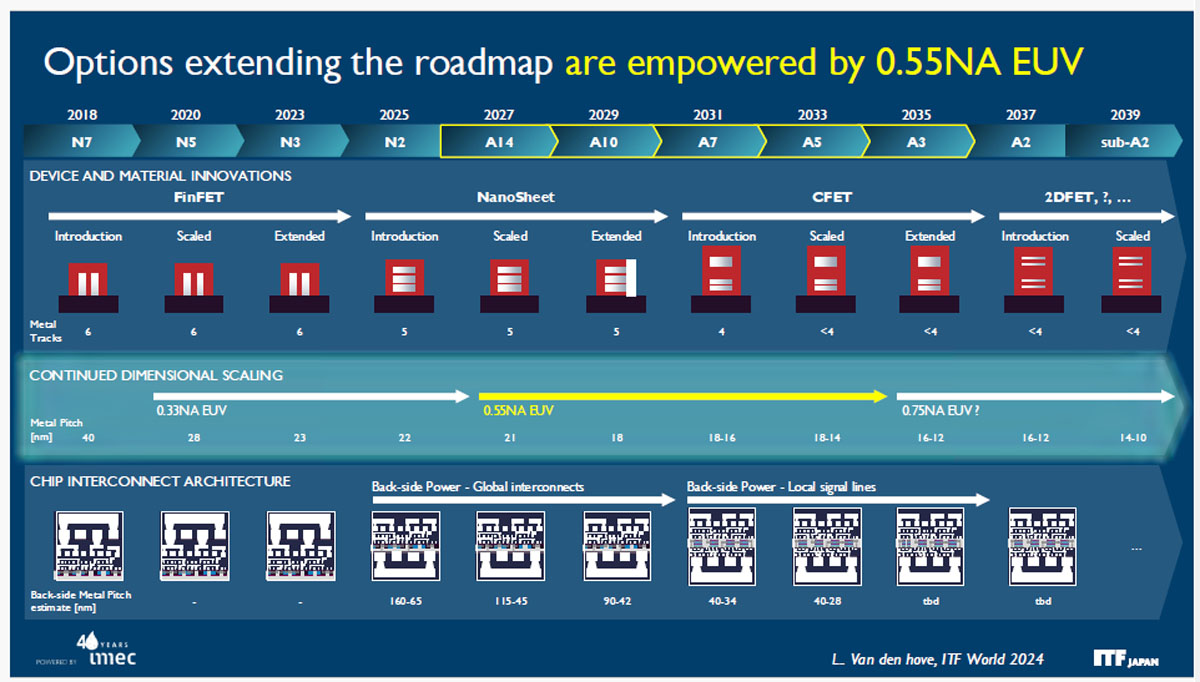

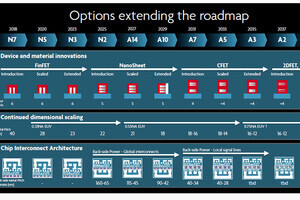

基調講演に登壇したimec CEOのLuc Van den hove氏は、「1965年にGordon Moore氏(当時は米Fairchild Semiconductor勤務、後にIntelを共同で創業)が示した、いわゆる『ムーアの法則』に従って、半導体チップの集積度が過去60年にわたって飛躍的に向上してきた。この間、ムーアの法則は間もなく終焉すると繰り返し言われてきたし、今も言われている。しかし、高NA EUV露光装置(ASMLのEUV露光装置「EXE:5000」、従来の開口数NA=0.33に対して高NA EUV露光装置はNA=0.55に引き上げれている)の登場で、ムーアの法則は、少なくとも2030年半ばまでは延命できる」とまだしばらくは継続できることを強調した。また、将来的にはNA=0.75のHyper-NA EUVリソグラフィ技術が開発され、加えてトランジスタのチャンネル部分をシリコンから2D(2次元)材料で置き換えた2D-FETが開発されれば、ムーアの法則はさらに2040年代に向けて延命されると、技術革新によって将来的に継続していける見通しを示した。

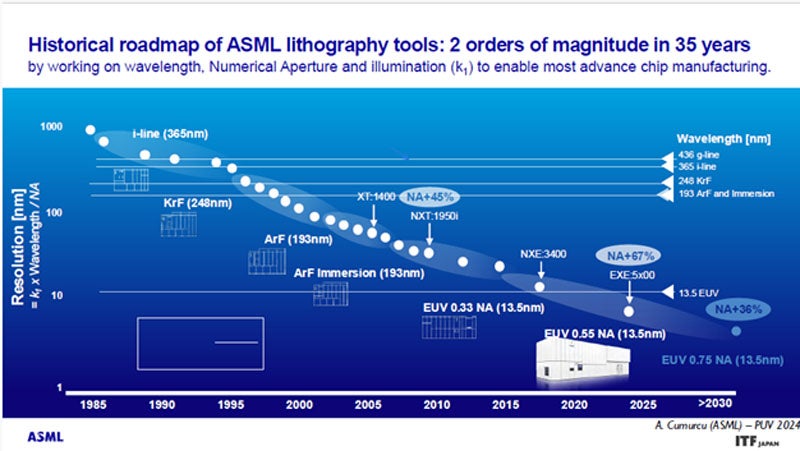

露光装置の歴史を振り返ると、さまざまな波長の露光装置が開発され、解像度が向上してきた。ASMLのみが製造できるEUV露光装置については、NAが0.33、0.55のものは製造ラインや試作開発ラインで利用が進んでいるが、NA=0.75のEUV露光装置はまだ開発されていない。

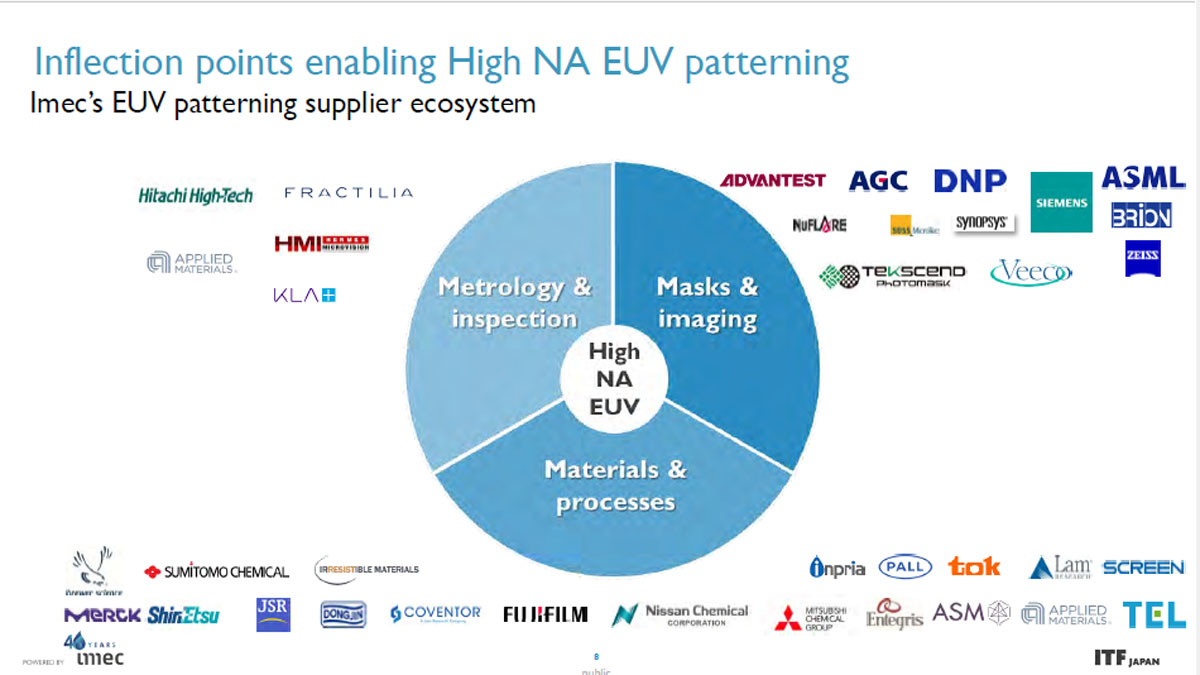

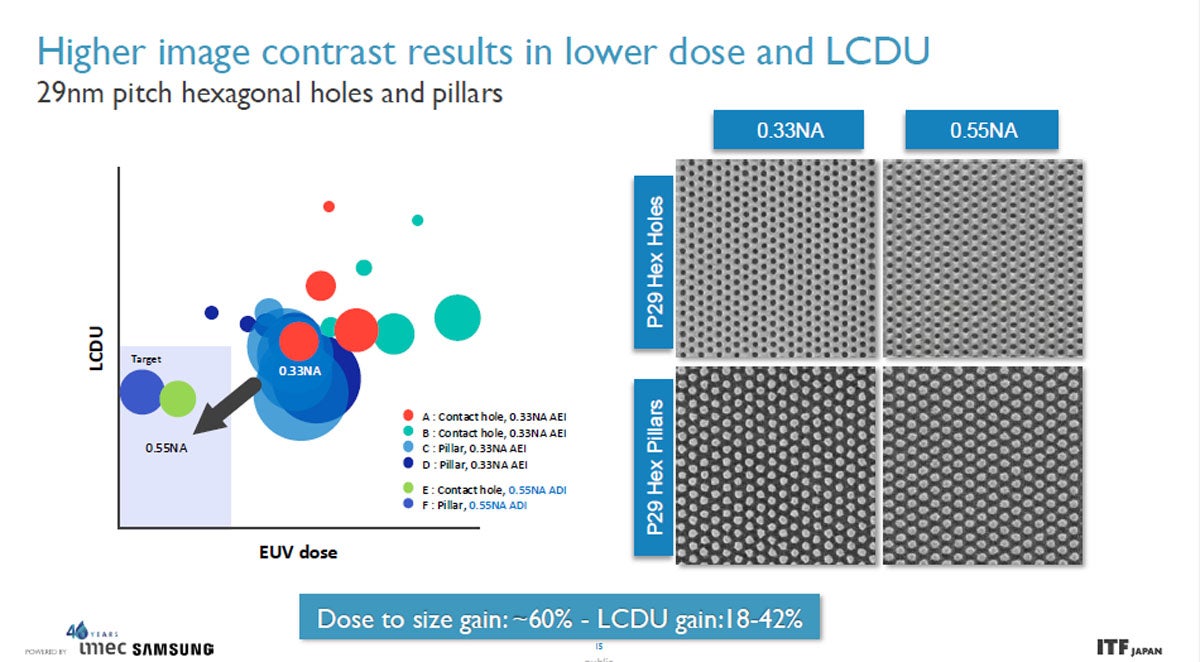

最新世代となる試作向け高NA EUV露光装置は現在、オランダのASML本社キャンパス内のimec-ASML High-NA Lab (imecとASMLの共同ラボ)内に設置され、世界中の約40のプロセス装置、計測装置、プロセス材料メーカー、マスクサプライヤなどと協業して、微細回路パターニングプロセス開発に取り組んでいる。NA=0.33のEUVに比べて高NA EUVは、高画像コントラストのため、EUVドーズ量が少なく、LCDU(Local Critical Dimension Uniformity:局所寸法均一性)が優れていることが分かったという。また、マルチパターニングの必要がないので、露光プロセスが簡素化し、製造コスト削減できる可能性があるともしている。

-

高NA EUVは画像コントラスが高いため、EUVドーズ量が少なくて済み、LCDU性能が向上するというイメージ(左)、NA=0.33およびNA=0.55のEUVリソグラフィにより形成した29nmヘックスピラーSEM像(右) (出所:imec)

imec本社キャンパスに高NA EUV露光装置の搬入を計画

imecの高NA EUV露光装置導入の第1段階をASMLとの協業に基づくオランダでのHigh-NA EUV Labでのパターニングプロセス開発とするならば、第2段階は、2025年にベルギー・ルーベンにあるimec本社キャンパスにある既存の300mmクリーンルーム「Fab3」への設置であるとVan den hove氏は説明している。

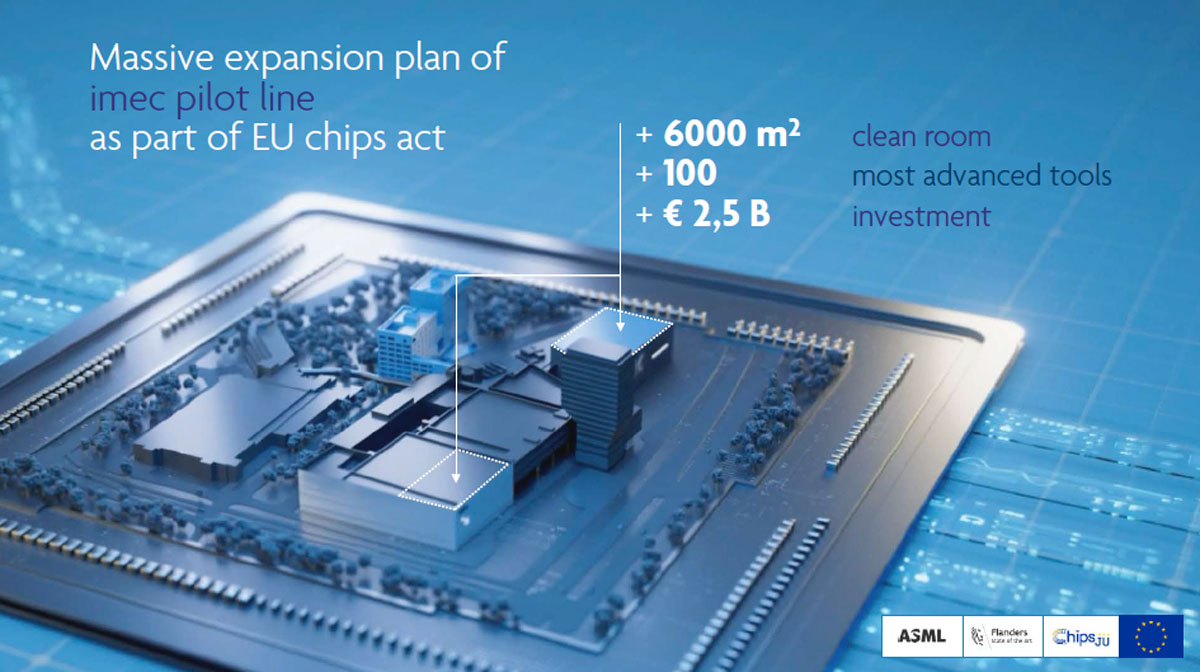

また、2026年までに、Fab3にすでに設置して活用している従来のN=0.33 EUV露光装置と、性能、スループット、プロセスコストなどさまざまな比較を行うことで特性の違いの理解を進める取り組みを第3段階とする。そして、第4段階として、2027年に新設の「Fab4」に高NA EUV露光装置の量産モデルとなる「EXE:5x00」を搬入して2nm超のロジックデバイス試作に活用することを検討しているという。

なおFab4というのは、既存の300mmクリーンルーム(FOUP手動搬送による研究・開発ライン)の隣接地に、EU CHIPS法(米CHIPS法の欧州版)に基づく25億ドル(公的資金は14億ドル、残りの11億ドルはASMLなどからの民間資金)を投じた2nm超デバイス試作用のクリーンルーム(imecにとっては初のFOUP自動搬送OHT採用)で、2025年以降の着工、試作開始を予定している。公式には、「NanoIC Pilot Line」と呼ばれ、EU CHIPS法に基づく欧州半導体強化プログラムの中核施設となる。imecや仏Letiや独Fraunhoferでの研究開発と半導体企業での量産の橋渡しの役割を果たすという。