理化学研究所(理研)は9月5日、量子コンピュータのための新たな量子誤り訂正符号「多超立方体符号」を提案し、誤り訂正技術を高効率化することに成功したと発表した。

同成果は、理研 量子コンピュータ研究センター 量子コンピュータアーキテクチャ研究チームの後藤隼人チームリーダーらによるもの。詳細は、米国科学振興協会が刊行する「Science」系のオープンアクセスジャーナル「Science Advances」に掲載された。

量子コンピュータは、従来型(古典)コンピュータとは異なり、0と1どちらかのビットだけでなく、その両者の重ね合わせの状態も取ることが可能(量子ビット)で、それを実現しているのが、量子力学における、複数の物理的な状態が重なり合った状態の「量子重ね合わせ状態」である。

しかし同状態は壊れやすいため、量子コンピュータは、古典コンピュータよりも高い確率で計算中に誤りが生じてしまう。そこで重要となるのが、誤り訂正技術となる。符号化によって守られた情報を表現する量子ビットのことを「論理量子ビット」といい、この論理量子ビットを用いることで誤りを訂正できるようにする仕組みを持ったものが誤り耐性量子コンピュータである。

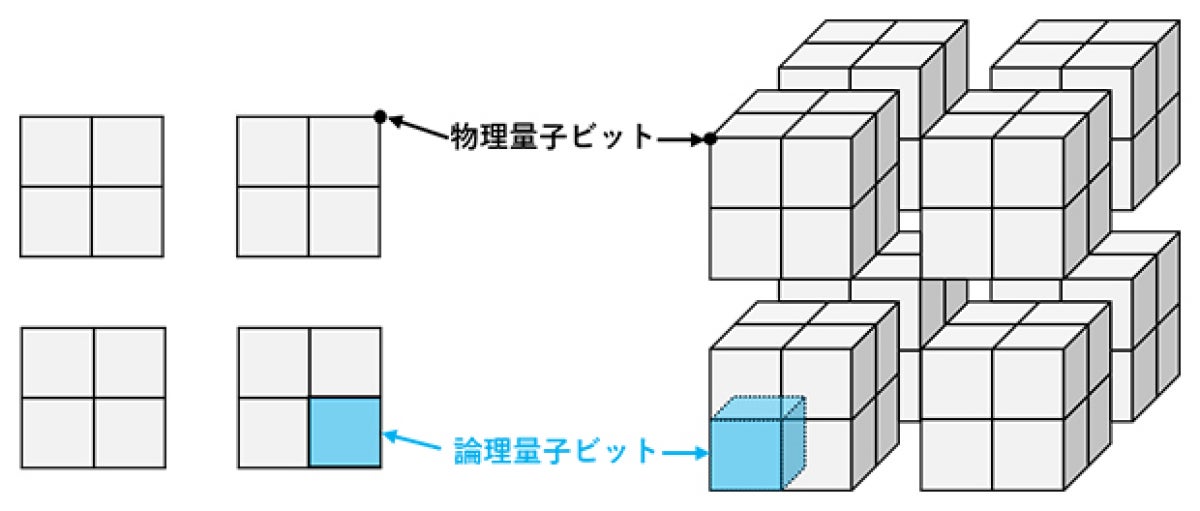

誤り耐性量子コンピュータは現在のところ実現できていないが、その理由がここにある。現在の標準的な量子誤り訂正符号では、論理量子ビットを1つずつ多数の「物理量子ビット」(量子コンピュータのハードウェア上に物理的に実装されている量子ビットのこと)に符号化するため、全体として物理量子ビット数が膨大になってしまい、誤り耐性量子コンピュータの実現を阻む大きな課題となっているのである。n個の物理量子ビットを用いて、k個の論理量子ビットを符号化する場合、比k/nをその符号の「符号化率(レート)」と呼ぶが、従来の量子誤り訂正符号では、たった1個の論理量子ビットを守るために多数の物理量子ビットを必要とすることから符号化率が数%以下と低く、非常に非効率だったのである。

そのような課題の克服のため、最近期待されているのが、多数の論理量子ビットをまとめて符号化できる高符号化率の量子誤り訂正符号(高レート符号)。しかし、これまでの高レート符号は符号の構造が複雑であり、従来の論理量子ゲートを並列に実行することが比較的困難という、別の課題が生じていたという。そこで後藤チームリーダーは今回、高い符号化率を有する新たな量子誤り訂正符号を提案することにしたとする。

-

多超立方体符号の構造の可視化。左は2次元の、右は3次元の多超立方体符号の構造を可視化したもの。頂点が物理量子ビットを、正方形(左)や立方体(右)が論理量子ビットを表す。一般に、n次元の多超立方体符号は6n個の頂点と4n個のn次元超立方体で表現される。次元が高いほど誤り訂正能力が高い(出所:理研Webサイト)

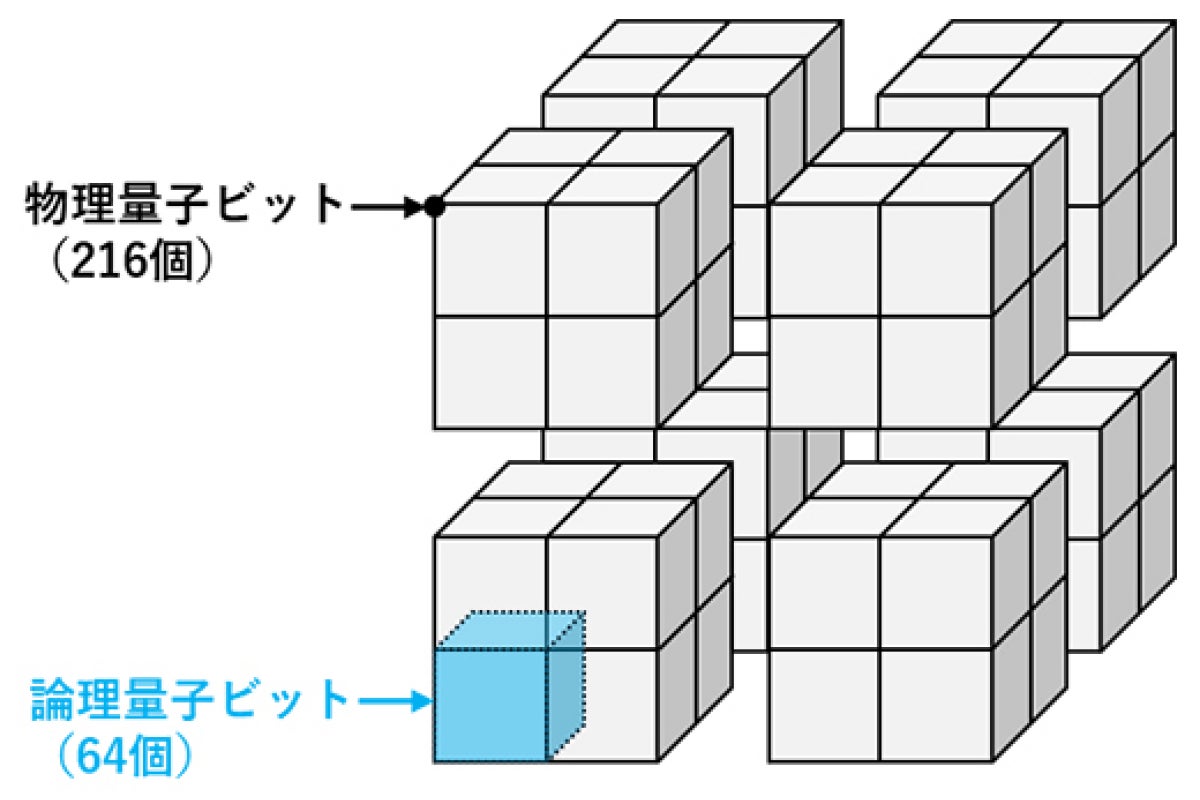

今回提案された多超立方体符号は、たとえば、6の2乗=36個の物理量子ビットを用いて4の2乗=16個の論理量子ビットを、または、6の3乗=216個の物理量子ビットを用いて4の3乗=64個の論理量子ビットをまとめて符号化することが可能。符号化率はそれぞれ16/36≒44%、64/216≒30%となり、代表的な従来符号のこれらに対応する符号化率がそれぞれ約6%、1.6%であるのに比べて高くできるという。

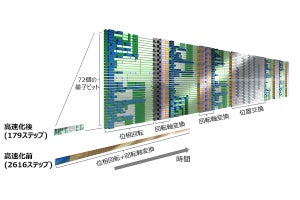

このように符号化率を向上させると、その結果として誤り訂正性能が下がってしまう心配があるが、多超立方体符号専用の高性能な「復号器」(測定結果から誤りを推定して訂正する方法または装置のこと)や、「符号化器」(符号化された論理量子ビットの状態を生成するために物理量子ビットに実行される一連の量子ゲート(量子回路)のこと)を新たに開発することで、従来符号と同程度の誤り訂正性能が達成された。

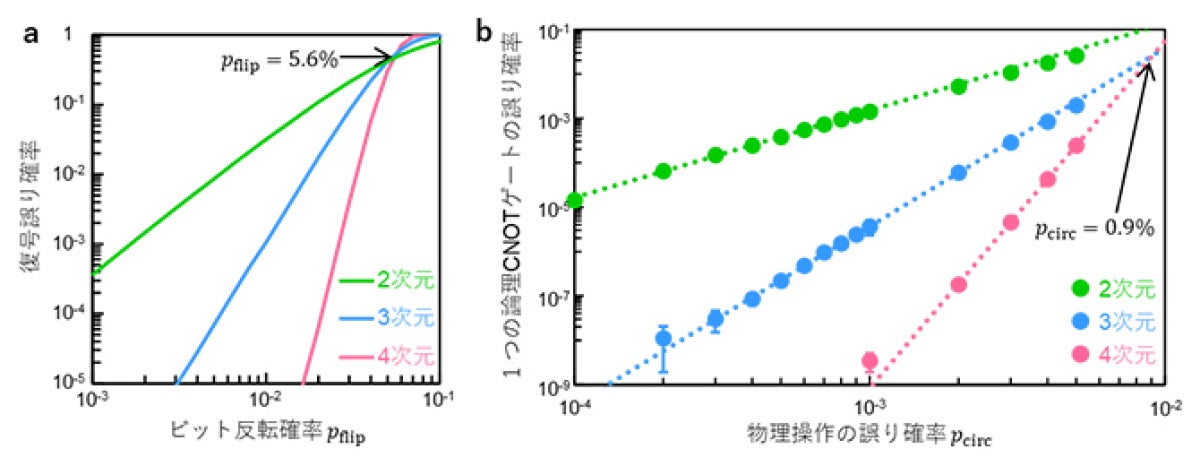

まず、復号器の性能が評価されたところ、その「しきい値」は5.6%となり、符号化率の低い従来符号と同程度となったとする。次に、符号化器も含めた性能を評価するため、論理量子ビットに対して実行される、任意の量子計算を実行するために必要な基本量子ゲートの一種である「論理CNOT(制御NOT)ゲート」の性能が評価された。すると、そのしきい値は0.9%となり、これも従来符号と同程度となったとした。なおしきい値とは、誤り訂正が有効に働くために必要な誤り確率の上限値のことをいい、誤り確率がしきい値未満であれば、符号のサイズを大きくするほど誤り訂正の成功確率が向上する。

-

数値シミュレーションによる多超立方体符号の性能評価。(a)理想的な符号化状態にビット反転誤り(「1」を「0」、「0」を「1」に誤って反転すること)を起こし、理想的な測定で得られる結果を今回開発された復号器で復号した結果が誤る確率。(b)物理量子ビットに対するCNOTゲート、および物理量子ビットの初期化と、測定に誤りがある現実的な誤りモデルにおいて、今回開発された符号化器を用いて生成される符号化状態を利用し実行される論理CNOTゲートが誤る確率(出所:理研Webサイト)

また、これまでの高レート符号では、その構造の複雑さから論理量子ゲートを並列に実行することが比較的困難なことが課題だったが、今回の研究では多超立方体符号に対して論理量子ゲートを並列に実行する方法を具体的に示すことで、論理量子ゲートの並列実行が可能であることが示されたとした。

今回の研究成果は、多超立方体符号を用いることで、これまで難しかった高符号化率を有する符号と論理量子ゲートの並列実行を両立する「ハイパフォーマンス誤り耐性量子コンピュータ」の実現に貢献できることが期待されるとしている。