インテルは「技術とビジネスをつなぎ社会を前進させる」をテーマとする「Intel Connection 2024」を9月3日と4日に開催している。初日の基調講演では、「AI Everywhere, The New Chapter」と題して、AIの進歩に欠かせない半導体技術を今後も発展させていくために、日本での取り組みを強化していく姿勢を見せた。

順調に開発が進むIntel 18A

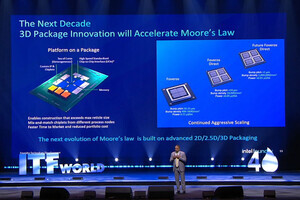

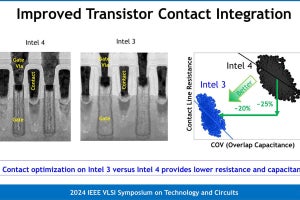

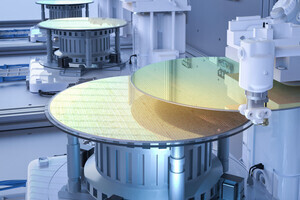

Intelは現在、4年間で5つのプロセスノード(4Y5N)の実現を目指し、急速にプロセスの微細化を進めている。すでに3世代目となるIntel 3(3nmプロセス相当)は量産を開始済み。次世代のIntel 20A(2nmプロセス相当)も製造準備を完了し、5世代目となるIntel 18Aについても自社開発のAI PC向けプロセッサ「Panther Lake」(開発コード名)およびサーバ向けプロセッサ「Clearwater Forest」(開発コード名)を使ったOSの正常起動が確認されるなど、順調に開発が進んでおり、2025年上半期には外部顧客の製品もテープアウト予定であるとする。

このIntel 18Aについて同社は、「PPA(Power-Performance-Area)の観点から最先端のプロセス技術」と表現。PDK 1.0のリリースなども含め、プロセス技術のみならず、設計を含めたトータルでの開発環境が整いつつあることを強調した。

量産に立ちはだかる課題突破の鍵を握る日本のエコシステム

こうしたプロセスの微細化は、いわゆるムーアの法則を維持するための重要な要素となってきたが、近年は微細化の物理限界の見えてきたこともあり、性能向上に向けて、新たな材料や技術の導入などが進められるようになっている。Intelの上級副社長 ファウンダリー技術開発本部 技術研究・外部研究開発連携 ジェネラル・マネージャーのサンジェイ・ナタラジャン氏は、「半導体が量産に至るまでに、基礎研究から社内R&Dに至る際に生じる障壁、いわゆる“Gap1(ギャップ1)”はこれまでもよく知られていたが、そこは世界各所で対処が進められてきた。しかし、近年は社内の試作から工場での量産に至るまでに生じる障壁“Gap2(ギャップ2)”が問題になってきている。この課題に対しては、半導体業界全体で協力して解決していく必要がある」と、問題の解決には多くのコラボレーションが重要となることを強調。今回の来日には、インテルファウンドリとして、日本のパートナーとの協力を推進していく役割を果たすためという側面もあるとした。

同社が日本のパートナーを重要視する施策の1つに、2024年4月に設立された半導体後工程の自動化・標準化を目指す技術研究組合「半導体後工程自動化・標準化技術研究組合(Semiconductor Assembly Test Automation and Standardization Research Association:SATAS)」がある。

Intelのファウンダリー技術開発本部 副社長 アナリティクス&テクノロジー オートメーション中央技術部 ジェネラル・マネージャーであるジェフリー・ペッティナート氏は、「半導体の後工程は自動化されている部分もあるが、マニュアルでの作業も多く残されている。そうしたマニュアル部分を自動化することで、生産性の向上を図ろうというのがSATASの目指すもの。工場のすべてを自動化して、効率よく搬送できる相互運用可能なメインフレームを構築することで、設備の柔軟性を高めていくことを目指して、SEMIとも協力して業界標準とすることを目指している」と、SATASとしての取り組みの意義を説明。前工程と後工程の工場を近くに作ることで、サプライチェーンのリスク低減にもつながるとする。

「自動化された後工程の標準化を目指すが、オペレーションや設備の運用などについての検証も行っていく」としており、2028年の商業化を目指す。日本に設置されるパイロットラインは4000m2の広さで、AMHS(自動搬送システム)が導入されるほか、プロセスセルや搬送用トレイ/キャリアなどを統合して、その実用性の実証が進められる予定だという。

SATASの代表を務めるインテル代表取締役会長の鈴木国正氏は、「インテルの社長をやり始めて以降、いろいろな形で日本法人とIntel本社が一緒に動く、Japan for Intelという言葉を使ってきたが、その象徴的な動きがSATAS」だと説明。対象範囲を明確にしながら、それぞれの分野を担当する日本企業に参加してもらいつつ、それらのコーディネートをペッティナート氏を中心に進めていくのがインテル/Intelの役割だとする。また、「後工程の重要性や自動化の話が出てきているが、SATASはあくまで業界全体のための取り組み。半導体業界は大きな課題を抱えながらも成長が続くことが期待されている分野。その課題の1つである後工程の標準化を図ろうというのが、この取り組みとなる」と、あくまでインテルのための取り組みではないとし、インテルならびにIntel合わせた19社・団体で協力して実現に向けた取り組みを推進していくとした。

日本の研究機関との連携で、次世代技術の研究開発を強化

Intel Federal社長 ジェネラル・マネージャーであるクリストファー・ジョージ氏は、「Intelでは、通常の半導体プロセスの微細化に向けた取り組みのみならず、次世代HPCやAI、量子システムの構築に向けた研究開発も行ってきた。そうした新たな分野の技術を実現していく中で、マテリアルエコシステムとして日本は重要なパートナー」と指摘し、理化学研究所(理研)や産業技術総合研究所(産総研)、東京大学(東大)などといった日本の研究機関との連携の重要性を強調した。

-

左からサンジェイ・ナタラジャン氏、Intel Federal社長 ジェネラル・マネージャーであるクリストファー・ジョージ氏、理研 計算科学研究センター センター長の松岡聡氏、東大 特別教授室 特別教授の黒田忠広氏

その理研の計算科学研究センター センター長を務める松岡聡氏は、「今のAIは数千億から1兆規模のパラメータでトレーニングしているが、それだと産業界が必要とするスパコンの世界を考えると限界が来る。スパコンでは、AIだけでなく第一原理計算シミュレーションなども実行されており、ゼタスケールの演算能力を目指す時代になっている。その際には量子計算も含まれることとなり、従来の計算から量子計算まですべてが一緒になる世界を作る必要がある」と指摘。現在の科学文明まで人類が発展できた背景には、サイエンスやエンジニアリングによる新たな発見や新技術の創出があり、AIがそうした本当の意味でのクリエイションができないと、限界がくるとし、科学データはこれまでの生成AIで必要とされたデータ量に比べて桁違いにデータ量が多く、そうしたデータをAIが活用できるようにしていくことが理研としての役割であるとし、2023年5月にIntelと理研が締結したAI、HPC、量子コンピュータなどの次世代コンピューティング分野における共同研究を加速させる連携・協力に関する覚書はそうした両者で協力していく意味合いがあるとする。

また、理研の現在のスパコン「富岳」の次世代機となる「富岳NEXT」の方向性として、「重要になるのはメモリ技術。メモリがイノベーションを生み出すことが重要」と指摘。こうしたイノベーションを生み出すことで富岳NEXTでは見たこともない価値の創出を目指すとしていた。

このメモリのイノベーションに関して東大 特別教授室 特別教授の黒田忠広氏は、「AI処理のボトルネックは演算処理よりもメモリにある」と説明した。

AIとシミュレーションの活用により、物理現象を仮想空間で実証し、その結果を物理現象に反映させる、いわゆるデジタルツインの活用が進むことが期待されている。黒田氏も「デジタルツインで実現するための物理空間と仮想空間の高度な融合が、さらなる半導体の発展のドライブになる。これが一言で言えばAIという存在になる」とし、物理空間の価値づけが比較的うまい日本と、仮想空間の価値づけがうまい米国、これからの時代に、両者が高度に連携する必要がある時代に突入するとの見方を示した。

その一方で、膨大は演算処理を行っていくためには膨大な電力を消費する必要があり、「2025年以降、世界のいたるところでエネルギー需要がひっ迫する。とりわけアジアがひっ迫する。これからの安全保障として、電力をいかに安定的に供給できるかという点と半導体の省エネ化が重要になる」とも指摘。AIサーバは従来サーバよりも電力を消費するとされているが、その内訳として割合の大きなものはGPUが30%、そしてDRAMが合計で48%を占めると試算されるとする。「DRAMのデータの読み書きだけで全体の10%の電力を消費する。GPUとメモリ間のデータのやり取りで19%、そしてDRAM内のデータ移動で19%。まさにフォン・ノイマン・ボトルネックであり、AI処理で頻繁にデータが移動することで、エネルギーの無駄遣いが頻繁に発生することになっている」とデータをいかに移動させないで処理することが今後、重要なポイントになってくるとし、メモリとプロセッサを可能な限り近くに配置するアプローチが求められるとする。

従来、DRAMとプロセッサは基板上の別々の場所に配置され、電気配線を介してやり取りをしていた。現在、帯域メモリと呼ばれるHBMがGPUと同じパッケージ上に設置されており、従来比では電力対性能比を向上させているが、両者間のデータ移動は2次元的なもので、この移動エネルギーのさらなる削減には、プロセッサ・イン・メモリの考え方もあるが、本質的にはプロセッサの上か下にメモリを持ってきてつなげる、いわゆる三次元実装(3D実装)が最適と考えられている。

その実現のためにシミュレーションソフトなども出てきているが、実際問題として各チップ/ダイから発生する熱が問題となる。3D化に伴って、熱密度が向上してしまい、それを解決できなければ、実用的ではない。「シリコンの基板は上手に熱を逃がせるが横に積むと、SiO2(絶縁層)が邪魔をして熱をこもらせるので、メモリチップを縦に100枚とか立てて並べるといったことも机上では考えられる。これを実現するためには研究開発が必要。その研究能力は日本にあるし、製造装置や材料も日本にある。日本は三次元実装で世界に貢献できるチャンスがある」と、半導体の3次元化は日本の半導体産業にとって、まさに好機到来であるとする。また、「AIの推進には3Dパッケージングが重要であり、Intelを中心に日本の企業やアカデミアが連携する時代がきた」と、デバイス-装置-材料という半導体エコシステムの構築が重要となることを強調した。

-

ロジックチップの上にメモリチップを積層すると、絶縁層が多層形成され、熱伝導を妨げるが、縦にメモリを並列に置ければ、絶縁層に邪魔されることなく熱を逃がすことができるという試算。これを実現するためには従来横方向で考えられてきたメモリの配線を縦方向に最適化したり、これまでとはまったくことなる半導体製造のアプローチが必要になることが容易に想像される

日米でEUVの先端研究を連携して推進

これらの話を受けたナタラジャン氏は、コラボレーションの重要性を強調。すでに日米の政府間での半導体研究開発コラボレーションが推進されているほか、Intelとして産総研と産総研子会社として2023年4月に設立されたAIST Solutionsとのパートナーシップを通じて、日本におけるEUVリソグラフィ研究開発センターの設立を支援していくことを明らかにした。また、日本のサプライヤやアカデミアとの連携によるリソグラフィプロセスにおけるPFASの除去などに向けた開発を推進していくことも示した。

こうしたIntelの日本重視の姿勢に対し、経済産業省 商務情報政策局長の野原諭氏は、「日本政府としても半導体政策を3つの目的で考えている」とし、半導体産業を日本の柱となる基幹産業の1つとして育てていくことを目指していることを明言。グローバルプレイヤーと協力して、日本での半導体製造、R&Dの推進、そして強みとなっている製造装置や材料を中心としたグローバルへの供給責任を果たしていくための支援を行っていくとし、Intelが日本にとって不可欠なパートナーであるとの見方を示した。

EUVリソグラフィ研究開発センターの設立に関しても、Intelが中核的な存在になることに対する期待を示し、同社のオレゴンのEUV研究拠点とも連携を図り、次世代製造装置の開発や日米アカデミア連携による高度な半導体人材育成にもつなげていきたいとするほか、PFASフリーの材料開発プロジェクトもEUV拠点連携との関係性強化に対する期待をのぞかせた。SATASについても、「政府としても、インテルと日本企業の連携した取り組みをサポートしていく用意がある」とし、インテルとともに日本ならびに世界の半導体産業の成長に向けた協力関係を構築していきたいとした。

また、このEUVリソグラフィ研究開発センターの受け口となるAIST Solutionsの代表取締役社長を務める逢坂清治氏は、「半導体は日本が世界に貢献できる重要な産業」であるとし、Intelと協力して導入に多額の費用が必要なEUV露光装置の利用体制を整備し、国内メーカーに提供することで、材料ならびに製造装置産業の下支えを含め、半導体産業の発展に寄与していくことを目指すとする。そのため、このプログラムに参加し、ともに研究開発を進めてくれるパートナーを広く募集していくとし、興味のある日本企業は積極的に声をかけてもらいたいとしていた。

-

産総研グループとして見た場合の半導体開発体制。以前から有するスーパークリーンルームはもとより、Rapidusと連携して先端プロセスを推進するLSTCや、設計支援に向けたOpenSUSIといった幅広い取り組みを近年は推進している。従来、LSTCでは2nm以降のデバイス開発に向けて必須となるEUV露光装置について、Rapidusのパイロットラインを借りる形で開発を進めていく予定としていたが、今回のIntelとの連携により、それとは別に新たにEUV拠点が設置されることとなる模様である

このほか、同基調講演にはアメリカ合衆国大使館 商務担当公使のアラン・ターリー氏も登壇。日米政府が協力して半導体サプライチェーンのレジリエンスの強化を目指していることを指摘。その中でもIntelは研究開発の核となっており、サプライチェーンのレジリエンス創出の柱にもなっているとし、今回の一連の連携が日米の半導体業界の象徴的な取り組みの1つになると思うとし、米国政府としても協力・連携の重要性は認識しており、多くの日本のパートナーにもレジリエントなしっかりしたサプライチェーンの一員になってもらいたいと思っていると語っていた。