Samsung Electronicsは7月9日、2nmファウンドリプロセスと同社独自の先進2.5Dパッケージング技術「Interposer-Cube S(I-Cube S)」を使用したターンキー半導体ソリューションを、日本のPreferred Networks(PFN)に提供すると発表した。チップの設計は、Samsungの元社員が創業した車載およびAI SoC専門設計受託会社の韓GAONCHIPSが担当するという。

-

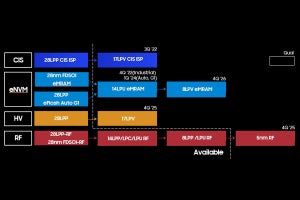

Samsung Electronicsの微細化技術ロードマップ。SF2(いわゆる2nmプロセス)は2025年量産開始予定 (出所:Samsung Foundry Forum 2024 U.S.発表資料)

-

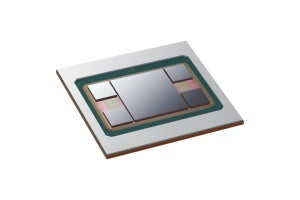

SamsungのI-Cube S技術 (出所:Samsung日本語Webサイト)

Samsungは、GAAアーキテクチャを3nmプロセスより採用してファウンドリサービスとして提供しているが、今回の契約により性能と電力効率をさらに向上させた2nmプロセスの受注に成功。先端プロセスの受注競争が激化する中、自社のGAA技術の完成度の高さをアピールするために発表したとみられている。

PFNは今回の契約により、Samsungの先端ファウンドリと高度なパッケージング技術を活用して、生成AIによって推進されるコンピューティング能力に対する高まる需要を満たす強力なAIアクセラレータの開発を目指すとしてる。

両社は今回の協業に基づいて将来、次世代データセンターと生成AIコンピューティング市場向けAIチップレットソリューションを紹介する予定だという。

PFNのコンピュータアーキテクチャCTOでVPの牧野淳一郎氏は、プレスリリースのエンドースメントとして、「Samsungの2nm GAAプロセスを採用したAIアクセラレータ技術をリードできることを嬉しく思う。このソリューションは、特に大規模言語モデルを中心とする生成AIの増え続けるコンピューティング需要を満たす、エネルギー効率に優れた高性能コンピューティングハードウェアを構築するというPFNの継続的な取り組みを大きくサポートするだろう」と述べている。一方のSamsung ElectronicsのコーポレートVP兼ファウンドリ事業開発チーム責任者であるテジュン・ソン氏は「今回の受注は、Samsungの2nm GAAプロセス技術と高度パッケージ技術が次世代AIアクセラレータの理想的なソリューションであることを証明した点で重要である。PFNと緊密に協力し、高性能と低消費電力の特性が十分に実現されるように努めている」と述べている。

なお、PFNがSamsung FoundryのSF2(2nmプロセス)の最初の顧客になるのではないかとのうわさが、2024年2月ごろから韓国半導体関係者の間で出回っていたが、今回の発表はそれを正式に認めたことになる。

2nmプロセスはSamsung、TSMCのほかIntelも推進しており、Rapidusも2027年には量産にこぎつけたい構えで、受注合戦は今後、激化していくことになりそうである。

2024年7月12日訂正:記事初出時、牧野淳一郎氏の役職名をコンピューティングアーキテクチャ担当VP兼最高技術責任者(CTO)としておりましたが、正しくはコンピュータアーキテクチャCTOでVPとなることから、当該部分を訂正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。