ウェハとウェハを接合するハイブリッドボンディングは、複数の集積回路チップを高密度で相互接続して3D積層する「高密度3D IC」を実現するための技術である。

この技術の適用領域をメモリ・オン・ロジックスタッキングなどに拡張するためには、3D相互接続ピッチを現在の最先端である1μmよりもはるかに狭める必要がある。

imecは、前例のない400nmまでの配線ピッチにおけるCuおよびSiCN間のハイブリッドCu・SiCN接合を実現し、その設計および技術革新についての説明を公開した。

ウェハ間ハイブリッド接合の適用範囲の拡大

3Dによる集積化は、マルチチップのヘテロジニアス統合ソリューションを実現するための重要なテクノロジーであり、システムレベルでのこれまで以上に高い電力、パフォーマンス、面積、コストの向上を実現するために、半導体業界全体で取り組んでいる次世代技術である。3D積層は、パッケージレベルからトランジスタレベルまで、電子システム階層のさまざまなレベルで導入されており、これまでにも多種多様な3D相互接続技術が開発され、幅広い相互接続ピッチ(数mmから100nm未満まで)に対応することで、さまざまなアプリケーションニーズに適用されてきた。この「3D相互接続のランドスケープ」を見ると、つねに技術進化が求められ、時間が経つごとにより小さな相互接続ピッチへの対応が図られてきた。

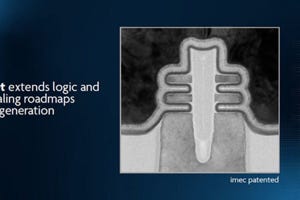

そして近年になって、高い相互接続密度と小さな相互接続寄生容量を可能とするウェハ間のハイブリッドボンディング技術が生み出された。このCu-Cuおよび誘電体-誘電体の接合技術では、Cuダマシン技術を使用して接合面を定義し、微細ピッチによるスケーリングを可能としている。

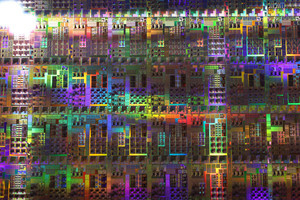

これまでウェハ間ハイブリッドボンディングの大量生産は主に、信号処理回路層上に積層されたイメージセンサの分野に限定されていたが最近は、同様の技術が3D NAND層とCMOS周辺回路の積層にも採用されるようになってきた。これらの商用アプリケーションは、約1μmという緻密なCu相互接続ピッチによって実現されており、1mm2あたり100万の相互接続を提供している。この技術のもう1つの資産は、異なる材料、機能、および異なる世代のCMOSテクノロジを組み合わせて使用することを可能としたということである。

今後数年間で、こうした技術の適用領域が拡大すると予想されている。システムと微細化技術の同時最適化(STCO)の進展を背景に、回路の分割は設計階層のさらに低いレベル、つまり回路ブロックやスタンダードセルにも及んできている。メモリ・オン・ロジック・アプリケーション(例えばロジック上のSRAM)の最初の発表はすでに行われており、これは高度なウェハ間ハイブリッド・ボンディング技術開発の主な推進力の1つとなっている。このような場合に、ウェハ間ハイブリッド接合の可能性を最大限に活用するには、研究者は相互接続ピッチを1μmを大きく下回るスケール化に成功する必要がある。

異種ウェハ間ハイブリッドボンディングのプロセスフロー

現在のウェハ間ハイブリッド接合プロセスフローはFEOL/BEOLを済ませた2枚の300mmウェハを用いて実施される。最初のフローは、オンチップBEOLダマシンプロセスに似ており、ボンディングされる誘電体(主にSiO2)を部分的にエッチングしてキャビティを形成する。これらのキャビティはバリアメタル、シード、Cuが充填される。続いて、ウェハ全体の高い均一性を実現するためにCMPが行われ、正確な位置合わせの後、2枚のウェハの接合を室温で実施。平坦化されたウェハ表面同士が接着された後、高温アニールが行われ、永久的な誘電体同士ならびにCu同士の接合がなされることとなる。

また、アプリケーション領域の拡大に伴い、ハイブリッドボンディングのより高度な実装も登場している。現状、ロジック・オン・ロジックまたはメモリ・オン・ロジックのスタッキングを可能にするために、ボンディングプロセスをフロントエンドにどんどん近づける傾向があるが、これには、より微細な相互接続ピッチが必要なだけでなく、ボンディングステップ後の後処理も必要となる。

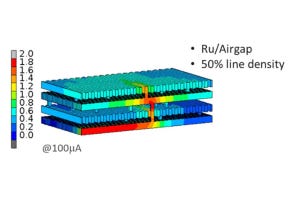

具体的な例としては、裏面電力供給ネットワーク(BSPDN)が挙げられる。BSPDNではウェハ間の接合が重要なステップであり、最初のウェハの前面がキャリアウェハに接合される。その後、最初のウェハの裏面を薄くし、n-TSVパターニング、金属充填、裏面メタライゼーションなどが行われるプロセスの流れだが、ここではBEOL処理の一部、つまり電力供給に役立つもっとも太い相互接続ラインの統合が、ウェハ接合プロセスの後に実行される点がポイントとなる。

これらのアプリケーションでは、現在のプロセスフローでスケーリングを進めようとすると、Cu間のアライメント精度、接合前のウェハ清浄度とトポロジー、および小さな相互接続ピッチでの誘電体とCuパッドの接合強度などの実現が求められることとなる。

ウェハ間ハイブリッドボンディングプロセスの改善で400nmピッチを実現

2023年のIEEE 国際電子デバイス会議(IEDM 2023)においてimecは、ウェハ間のハイブリッドボンディングのさまざまな側面を調査した包括的な研究結果となる400nm相互接続ピッチへの道を切り開く重要なイノベーションを報告した。

imecの研究チームでは、正方形または円形のパッド設計を備えた従来の正方形グリッドの代わりに、六角形グリッドと円形のCuパッドを備えたテストべヒクルを提案している。この新しい設計の利点として、Cuパッドを可能な限り高密度に配置しつつ、隣接するすべてのパッド間の距離を等しくすることができるようになることから、Cuパッドのサイズと間隔を最大化しながら、Cuパッドの密度を制御することが容易になる点が挙げられる。また、等しいパッド設計を使用した場合と異なるパッド設計を使用した場合の影響も調査したところ、後者の場合、上部ウェハは下部ウェハよりもぎりぎり小さいCuパッド寸法で設計されることとなるが、不均等なパッド設計には、ボンディングオーバーレイ許容差の向上、寄生容量の低減、小さな相互接続ピッチでの絶縁破壊強度の向上など、いくつかの利点があることが確認された。

また、信頼性の高いハイブリッド接合プロセスを実現するには、2枚のウェハを接合する前に、両方のウェハの表面が極めて平坦かつ清浄であることが求められることとなり、CMPが重要なプロセスステップとなること、ならびにCuパッドの均一な凹みも形成する必要があることも示された。さらに、アニール後にボイドのない接合を得るために、接合前にCuを誘電体表面から数nm下に残す必要があることから、研究チームでは、レイアウト設計において高度なCMPプロセスとダミーパッドを組み合わせることで、ウェハ全体にわたるCuパッドの高さと表面トポロジーを正確に制御することに成功したとする。

SiCN誘電体により接着強度と拡張性を向上

imecではこれまでの研究から、小さな配線ピッチに最適な誘電体としてSiCNを提案してきた。SiCN表面は、SiO 2表面と比較して高い結合エネルギーを示すからである。これは、結合を切断するのにより多くのエネルギーが必要であることを意味しているほか、SiCNはCuおよびウェハパッシベーション層の拡散バリアとしても機能し、ガス拡散をブロックし、熱的により安定した接合界面をもたらすこととなる。

これらの特性は、ハイブリッドボンディングの相互接続ピッチを調整する際にますます重要になる。結合強度を評価するための新しい技術であるナノインデンテーションに基づく測定により、SiCN-SiCN結合強度がSiO2-SiO2結合強度を上回ることが確認されたほか、 250℃で接合後アニール後に高い接合強度が得られ、それ以上の温度でも劣化しないことも判明した。

これらの洞察は、高度なウェハ間のCu/SiCN接合プロセスを実行するために行われたものだが、実際の接合は、プロセスの成功に不可欠なツールである高度な位置合わせ機能を備えた市販の高品質ウェハボンダを使用することで300mmウェハの接合に成功し、前例のない400nmピッチのCu相互接続を実現した。

このほか、ボンディングオーバーレイと信頼性(すなわち、絶縁破壊と歩留まり)との関係も調査したところ、小さい相互接続ピッチでは、等しく設計されていないCuパッドの方が、等しく設計されたパッドよりも高い絶縁破壊強度を有していることを確認したほか、これらの400nmの相互接続ピッチでは、大量生産で十分な歩留まりを得るためにはオーバーレイ制御を100nm未満にする必要があるとの結論を得るにいたった。この結果は、将来の3D SoC設計ニーズを満たすには、次世代のウェハ接合装置のオーバーレイ精度に厳しい要求が課せられることを意味すると考えている。

-

図3:Cu-Cu接続性の評価に使用される、等しいパッド設計の400nmピッチの長さのデイジーチェーンの拡大表示 (IEDM 2023で発表)。結果は、Cu/SiCN表面トポグラフィの制御に成功し、正確な位置合わせ(オーバーレイが150nm未満)および良好な電気的性能(低い単一接触抵抗)を示したとする (出所:imec)

400nm相互接続ピッチのその先へ

ウェハ間ハイブリッドボンディングは、増加し続けるI/O密度と機能ダイ間のより効率的な接続を可能にする有望な3D統合テクノロジとして期待されるようになっている。メモリ・オン・ロジックのようなアプリケーション(ウェハ間の接合がフロントエンドの近くで行われる)を可能にするには、Cu相互接続ピッチのスケーリングを究極の限界まで押し上げる必要がある。また、グリッド設計の改善、表面トポグラフィの制御の強化、誘電体としてのSiCNの使用、接合メカニズムの基本的な理解、およびオーバーレイ制御の改善が400nm以降の微細ピッチで電気的に機能的で信頼性の高いCu相互接続を実現するための重要な要因となるという今回の結果は、さらに微小な相互接続ピッチを備えた将来のウェハ間接合プロセスを開発するための基礎になると考えられる。

本記事はimecの「Wafer-to-wafer hybrid bonding: pushing the boundaries to 400nm interconnect pitch」を許可を得て翻訳したものとなります

|

Soon Aik Chew

imecの3Dシステム集積技術のプリンシパルスタッフメンバー。2001年にマレーシアのセインズ大学で修士号を取得。imecに入社する前は、ASE、Silterra、SSMC、およびAlteraでプロセスおよびデバイスの開発に取り組む。2011年9月のimec入社以降は、CMOSデバイスのミドル・オブ・ライン(MOL)テクノロジーに取り組んでいる。現在の研究は、ウェハ間のハイブリッドボンディング技術に焦点を当てたものとなっている |

|

Joeri De Vos

imecの3D IC集積チームの責任者。1991年に電気工学の学士号、1999年に応用科学の博士号をベルギーゲント大学より取得。2000年からimecに勤務しており、フラッシュメモリ、CMOSイメージセンサおよび3D IC集積に関する長年の経験を有している。現在、籍を置く3D IC集積チームは、ウェハ間のハイブリッドボンディング、BSPDN、およびインターポーザテクノロジのスケーリングに重点を置いた活動を行っている |

|

Eric Beyne

imecシニアフェロー、研究開発担当副社長、imec 3Dシステム統合プログラムディレクター。ベルギーのKUL(ルーベンカトリック大学)から1983年に電気工学の学士を取得、1990年には応用科学の博士号も取得。1986年よりimecに勤務、高度なパッケージングと相互接続技術に取り組んできた |