Applied Materials(AMAT)とウシオ電機は12月12日(米国時間)、3D ICパッケージ向けチップレットやヘテロジニアスインテグレーション(HI)のロードマップを加速することを目的とした戦略的パートナーシップを締結したことを発表した。

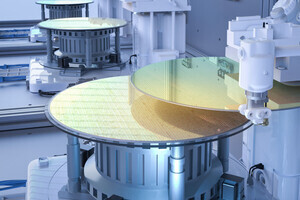

半導体のさらなる高性能化に向けた2.5D/3Dパッケージングの活用に注目が集まっているが、さらなる先端パッケージ技術の実現に向け、極細配線や優れた電気・機械特性が得られる、例えばガラス基板のような新材料を活用した大型パッケージ基板の採用に向けた模索が進められており、今回の戦略的パートナーシップは、この動きを加速させるために交わされたものであると両社では説明しており、次世代コンピューティングに求められる先進的基板をパターニングするために特別設計されたデジタルリソグラフィ装置(DLT)を共同で市場投入するとしている。

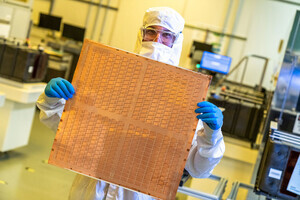

この新たなDLT装置は、量産レベルのスループットを実現しながら、先進的基板アプリケーションに求められる解像度を達成できる露光装置となることを目指したもので、具体的には線幅2μm以下のパターニングに対応し、ガラスや有機材料製の大型パネルや、ウェハを含むあらゆる基板上のチップレット設計において、最適な解像線幅を実現することができるという。また、予想外の基板の反りという課題を解決しながらオーバーレイ精度を実現することを目的とした独自設計も採用したという。

なお、この新たなDLT装置はすでに量産適用可能なモデルが複数顧客に向けて出荷済みとなっており、ガラスその他の先端パッケージング基板上で2μmのパターニング製造実証が進められているという。

また、今後についてAMATでは、ウシオ電機と共同で研究開発と拡張的なロードマップの定義を行い、線幅1μm以下の先端パッケージングに向けた継続的なイノベーションの推進を行っていくとしているほか、ウシオ電機側も長年培ってきた製造技術およびカスタマーサポートのインフラを活用してDLTの採用を促進していくとしている。