Cadence Design Systemsは9月13日(米国時間)、オンデバイスおよびエッジのAI演算処理に関して高まる需要に対応する次世代AI向けIP「Cadence Neo Neural Processing Units(NPUs)」およびソフトウェアツール「NeuroWeave SDK(Software Development Kit)」を発表した。

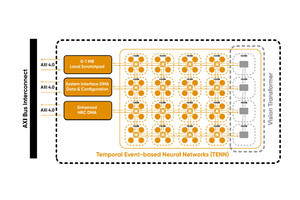

Neo NPU IPは、同社の第1世代AI IPと比較して、最大20倍の高速化と、IPS/mm2(1秒間、1mm2当たりの推論性能)も2倍から5倍、IPS/W(1秒間、1W当たりの推論)も5倍から10倍向上することに成功。シングルコアで8GOPSから最大80TOPS、マルチコアの場合、数百TOPSのパフォーマンスを提供し、新旧さまざまな生成AIモデルに対応することが可能だという。また、AMBA AXIインタコネクトを介してアプリケーションプロセッサ、汎用マイクロコントローラ、DSPなどといったホストプロセッサからAI/ML(機械学習)の実行をオフロードすることで、サイクル当たり256から32K MACに対応し、SoC設計者がPPA(Power、Performance and Area)条件を満たすよう組み込みAIソリューションを最適化することが可能になると同社では説明しており、これによりSoC設計者が最適なAI推論ソリューションをインテリジェントセンサ、IoTおよびモバイルデバイス、カメラ、ヒアラブル/ウェアラブル、PC、AR/VRヘッドセット、ADAS(先進運転支援システム)などといった製品に統合することを可能にするとしている。

一方のNeuroWeave SDKは、Tensilica DSP、コントローラ、Neo NPUを共通にサポートし、スケーラブルで設定変更が可能なソフトウェアスタックを提供することによってターゲットアプリケーションに対応し、製品開発の効率性を高め、進化する設計要件に応じた容易な移行を可能にするとのことで、TensorFlow、ONNX、PyTorch、Caffe2、TensorFlow Lite、MXNet、JAX、その他の業界標準の多くのドメイン固有なMLフレームワークに対応し、自動化されたエンドツーエンドのコード生成、Android Neural Network Compiler、リアルタイム実行に向けたTF Lite Delegates、マイクロコントローラクラスのデバイスに向けたTensorFlow Lite Microにも対応するなど、AI向けハードウェアの補完を可能とし、それによりコーディング不要なAI開発を実現することができるようになるという。

なお、Neo NPUおよびNeuroWeave SDKは、すでに一部の主要顧客にはアーリーアクセスとして提供済みで、一般向けには2023年12月初めより提供を開始する予定としている。