シャープは8月7日、同社の創業111周年記念イベント「SHARP Tech Day」を11月11日に開催するにあたって、先行イベントとして近年、世界的に注目を集める「半導体」をテーマとした「SHARP Tech-Forum」を開催した。

基調講演には鴻海グループの最高半導体戦略責任者である蔣尚義(Shang-Yi Chiang)氏が登壇。「集積回路から集積チップレットへ」をテーマに、これからの半導体技術がどのように変革していくかについての説明を行った。

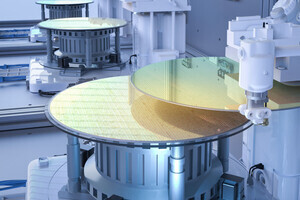

-

鴻海グループの最高半導体戦略責任者である蔣尚義(Shang-Yi Chiang)氏。同社入社以前はTSMCで250nm~16nm FinFETまで研究開発を主導していたほか、その前はHPやTexas Instruments(TI)の半導体事業に従事していた経歴を有している

蔣氏は現在を「50年以上の歴史を持つ半導体にあって、もっとも大きな変化の時を迎えている」と説明。そこには課題もあれば、チャンスもあるとする。

最大の課題はムーアの法則の物理限界が見えてきた点。これまで、半導体産業はプロセスの微細化を進め、トランジスタの集積度を向上させ、高性能化と低消費電力化、そして低コスト化を実現してきた。しかし、現在、最先端プロセスがコマーシャルプロセスで、その数値がそのままの素子の大きさにつながらないまでも、4nmや3nmといった値に到達している。「どうしても原子は0.5nmの大きさは必要になる。物理限界そのものが近いことに変わりはない。これはこの50年以上にわたる半導体業界にとってなかった大事件である」(同)とするほか、微細なプロセスの設計・製造に必要となるコストも上昇していることを指摘。「例えば4nmプロセスでは、フォトマスク1つとっても1500万~2000万ドルほどかかる。もし、テープアウトしても、回路がうまく機能しなかったら、再び2000万ドルを費やす必要があり、担当エンジニアやデザイン会社は神経質になっている」と、そのコストが半導体メーカーにとって大きな負担になっているとする一方、これまで培ってきた技術を変更することもリスクとなり、その見極めが重要になっているとした。

1ダイでの集積から1チップでの集積へ

2009年、TSMCの研究開発チームを率いていた同氏は、GPUとメモリの接続距離を短くすることができれば、さらなる高性能化が可能だということを考え、シリコンインターポーザーを活用した先端パッケージの開発を開始したという。それが現在、TSMCが提供する3次元パッケージ技術の1つ「CoWoS」の原型になったという(CoWoSの実用化は2011年)。

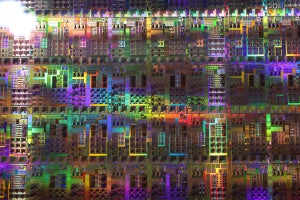

-

旧来のGPUカードではプリント基板上に設置されたGPUと8つのDRAMが基板上の配線を通じてデータのやり取りをしていたため、サイズや消費電力、バンド幅などの課題があった。これをシリコンインターポーザーを介して1チップ上に集積することで、データのやり取りの距離が短縮され、サイズや消費電力の削減が可能となった

これからの時代において、こうした3D IC技術はより重要度を増していくと同氏は指摘する。「これまでの半導体産業はメインフレームから、PC、携帯電話、スマートフォンといったように、単一の製品市場に多くの企業が参入して、そこの市場を支配する半導体メーカーが大量のチップを供給してきた。しかし、AIoTの時代が到来すれば、多様化が進み、そうした1つの規格に沿った半導体が搭載されるのではなく、それぞれのニーズに応じた少量多品種の半導体が必要になる。そうなると、数を売るという半導体のビジネスそのものを維持することが難しくなる。ICを手掛ける者の黄金律として、これまでは複数のチップを1つに集積することで、高性能化を果たせるというものがあった。しかし、ニーズが多様化し、プロセスも多様化した現在、チップは分割した方が良いという方向性に向かっている」と、3D ICの実用化が技術の転換点となったとする。

また、「特にアナログ半導体のプロセスシュリンクは難しい。プロセスの微細化はデジタルの人は喜ぶが、アナログの人が喜ぶとは限らず、むしろ苦悩する。チップレットの概念はこうした流れで生まれた。1つのチップを2つに分けたらどうか。これはたまたま生み出された概念と言える。CoWoSの研究を始めた当時は、そうした性能改善などがパッケージ技術によって得られるとは思っていなかったためだ」と、チップレットによって、プロセスが異なる半導体をニーズに応じて柔軟に選択して1つのパッケージに搭載していくことが、少量多品種の時代にマッチしたモデルであり、それにより半導体の設計・開発コストや、そこで動くアプリケーション開発コスト、最終的なシステムの開発期間の短縮なども可能となることを強調。「ほとんどの市場でタイムツーマーケットは重要であり、そのためには、コストの削減を図りつつ、プロトタイプを高速に開発できる環境が必要となる。チップレットはそれを可能にする技術となる」とチップレットの重要性を説明する。

-

多様なニーズに基づくIoT機器では、さまざまな機能の統合が求められるが、必要に応じて、それぞれの機能を変える必要があり、1ダイでそれを実現しているとペイできる規模でのビジネスが難しい。しかし、チップレットダイバンクを用意し、ニーズごとに各機能のチップレットを選択し、それを組み合わせることで半導体チップは規模のビジネスを維持しつつ、少量多品種ニーズにもこたえることができるようになる

ただし、「チップレットがすべてを置き換えるわけではないという点にも注意する必要がある」ともする。「チップレットの利点は、システムの高性能化という方向性と、システムの柔軟性を増すという方向性。これらを実現するためには、エコシステム全体を構築する必要がある。1社だけではそれは成しえないので、誰しもがパートナーとなって協力していく必要があり、そうしたエコシステムを構築できだものが最終的な勝者になる」としつつも、あくまでチップレットという技術は、次なる半導体のイノベーションが生み出されるまでのつなぎの技術であると説明。「半導体産業が待っているのは、その先にあるイノベーションである」とし、それを生み出せるのは、半導体産業に関わる若い技術者たちであり、そうした若い力による新たな半導体の価値創出に期待したいとしていた。