今回の研究のポイントは、確率動作スピントロニクス素子からなる高性能Pビットを、大規模な演算が可能なFPGAと組み合わせた点にあるという。FPGA上には、最大7085個のPビットを疑似的に実装することができる。これを、電力を消費することなく自然な熱によって状態が更新されるスピントロニクスPビットで駆動することにより、高度な計算が可能となった。いわば、半導体回路上に作製された大量の低性能な疑似乱数発生器を、スピントロニクス素子の力で性能の高い物理乱数発生器に変えることで、高度な計算を可能にしたようなものだとした。

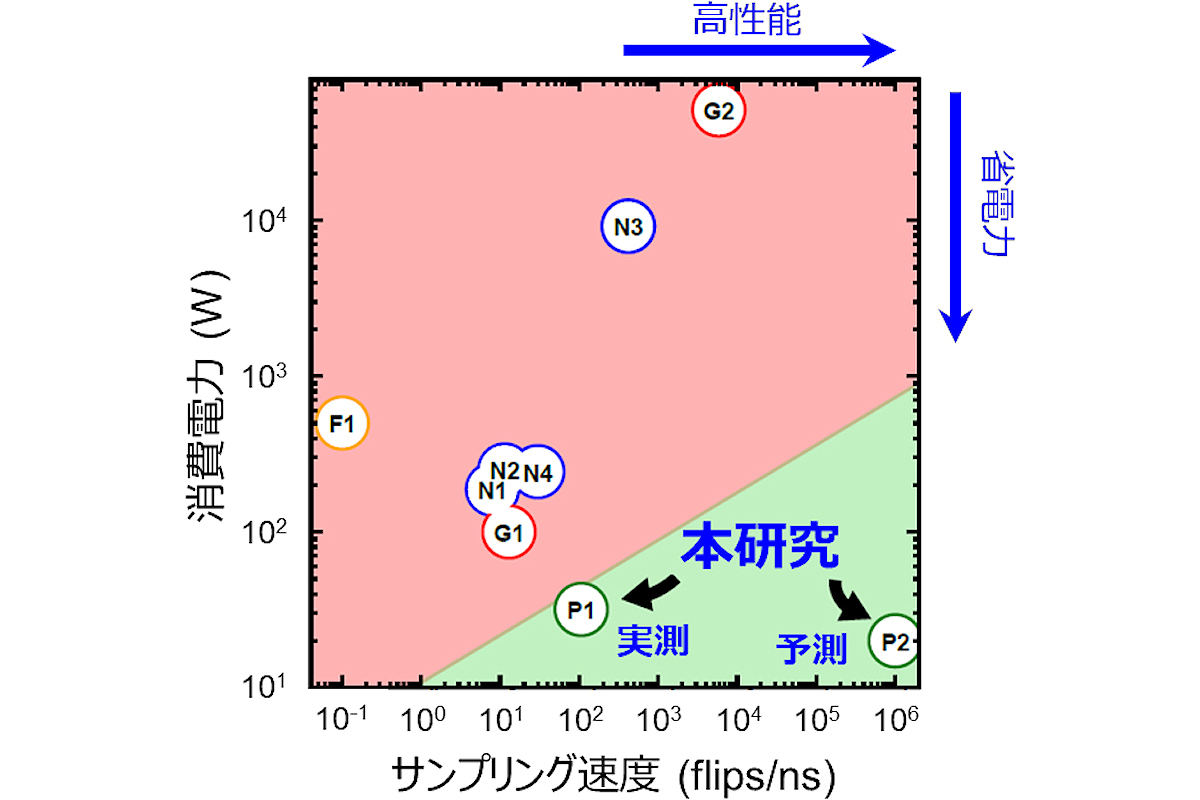

次に、Pコンピュータの消費電力が測定され、古典コンピュータで確率的なアルゴリズムを用いて演算を行う場合との比較が行われた。FPGAを用いたPコンピュータは実測値ベースで演算性能が106.28flips/ns、消費電力が32.72Wで、すでに古典コンピュータの典型値と比べて演算性能は2~10倍ほど高く、消費電力は1/3~1/10ほどまで抑えられていることが確認された。

加えて、研究チームは2021年に、超高速で熱による状態更新が可能なスピントロニクス素子を開発済みで、同様のスピントロニクス素子は、磁気抵抗メモリにおいてすでにメガビット以上の規模で量産されている。これらの技術を適用して専用集積回路を作製した場合に予測される値は、演算性能が約100万flips/ns、消費電力が20Wほどだった。つまり、演算性能はさらに4桁向上、消費電力はさらに約40%低減し、古典コンピュータの典型値を演算性能で約5桁、消費電力で約1桁凌駕する特性が得られることが明らかにされた。

-

Pコンピュータと、古典コンピュータで確率的アルゴリズムを実行した場合の、計算性能(サンプリング速度:横軸)と消費電力(縦軸)の比較。P1は今回の研究での実測値であり、P2はすでに確立されているスピントロニクス素子技術・集積化技術を用いた場合に予測される値。N1~N4はGPUコンピュータを用いた場合、G1~G2はTPU(Tensor Processing Unit)コンピュータを用いた場合、F1はシミュレーテッド・アニーリングコンピュータを用いた場合の報告値(出所:東北大プレスリリースPDF)

研究チームは、これらの予測値を今後実際に専用集積回路において実現するためには、材料・素子・回路・アーキテクチャ・アルゴリズムの全階層において、いくつかの技術課題に取り組んでいく必要があるとした。