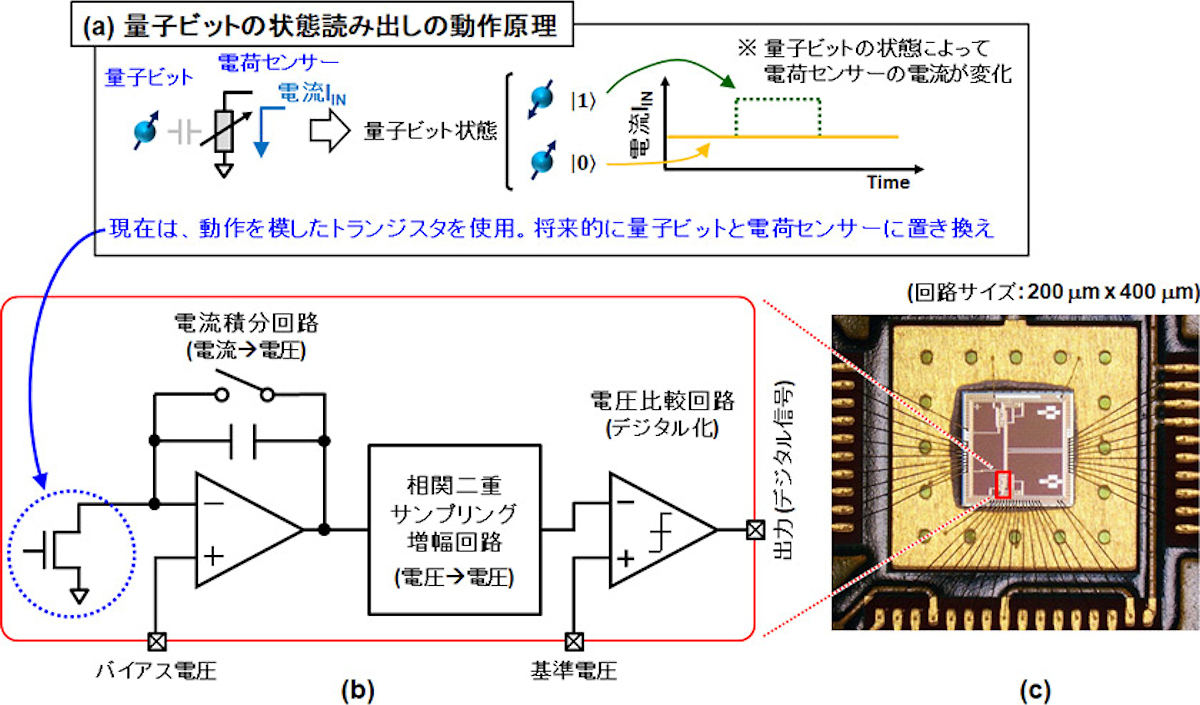

その結果、4Kでも動作する電流計測回路が開発され、電流の計測を極低温の冷凍機内で行い、量子ビット・電荷センサとの配線を短縮することで、高速読み出しを実現したという。

今回開発された電流計測回路は、(1)積分回路で計測する電流が電圧に変換、(2)積分回路の出力に対して相関二重サンプリングを実施、(3)その出力を基準電圧と比較して、スピン量子ビットの状態(スピンの向き)を表すデジタル値の出力(例えば、スピンの上向きはデジタル値0、下向きはデジタル値1など)という3つの回路ブロックで構成されるとする。

産総研におけるこれまでの極低温トランジスタ特性の評価から、極低温ではフリッカ雑音が増大することが報告されており、その影響で読み出し時間が増加する恐れがあったことから、その対策として今回の研究では新たに、(1)の積分回路の出力に対して実施する(2)の相関二重サンプリングを採用したとする。今回の回路では、量子ビットと電荷センサの代わりに、その動作を模したトランジスタが使用されているとする。

最終的に、開発された回路が一般的な商用CMOS半導体プロセスで製造され、4Kに冷却した状態で測定可能な独自の評価基板を用いて評価が行われたところ、計測可能な電流値と測定時間はトレードオフの関係にあることから、開発された電流計測チップを使用することで、電流値一定の条件で従来よりも100倍高速に計測することが可能であることが確認されたとする。

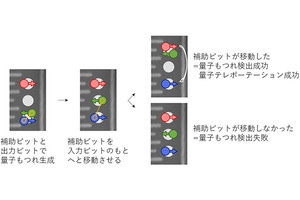

なお、研究チームでは今後、今回開発された電流計測回路とスピン量子ビット・電荷センサを接続し、量子ビットの状態読み出し動作を検証する予定としている。