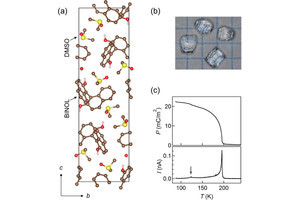

東京大学(東大)と奈良先端科学技術大学院大学(NAIST)は、酸化物半導体の「酸化インジウム」(In2O3)を従来のスパッタ法ではなく、「原子層堆積(ALD)法」で成膜する技術を開発し、三次元垂直チャネル型の強誘電体および反強誘電体トランジスタメモリの開発に成功したと発表した。

同成果は、東大 生産技術研究所の小林正治 准教授、NAIST 先端科学技術研究科の浦岡行治 教授の共同研究チームによるもの。詳細は、米国ハワイ州ホノルル現地時間6月11-12日に開催された国際会議「2022 IEEE Symposium on VLSI Technology and Circuits(VLSIシンポジウム)」のサテライトワークショップ「IEEE Silicon Nanoelectronics Workshop 2022」にて発表された。

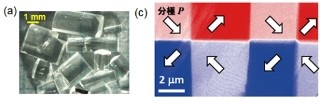

大容量ストレージメモリとしてはNANDが一般的だが、消費電力が大きいためIoTデバイスへの搭載には不向きとされている。一方で強誘電体トランジスタ(FeFET)メモリは、強誘電体の性質から消費電力は小さいものの、NANDのように高密度な三次元垂直チャネル構造を実現できるかどうかはわかっていなかったという。

特に、3D NANDのようにチャネルにポリシリコンを用いると、ポリシリコンの低移動度による読出速度の低下や、強誘電体とポリシリコンの間に低誘電率の界面層が形成され電荷捕獲による信頼性劣化や書込電圧が低くできなくなる、といった課題があり、こうした課題解決に向け、小林准教授らの研究チームはIGZOなどの酸化物半導体をチャネルとするFeFETメモリを提案し、理論的にその実現可能性と有用性を示してきたという。しかし、酸化物半導体を三次元構造へ均一に成膜するには、従来のスパッタ法では成膜の直進性が高く難しいという技術的な課題があり、ALD法での実現が望まれていたことから、今回、共同研究チームは、In2O3をALD法で成膜する技術を開発することにしたという。

2022年6月20日訂正:記事初出時、発表研究機関の表記、ならびに発表者の1人である浦岡教授の所属を北陸先端科学技術大学院大学と誤って記載しておりましたが、正しくは奈良先端科学技術大学院大学となりますので、当該部分を訂正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。