フラッシュメモリも積層へ

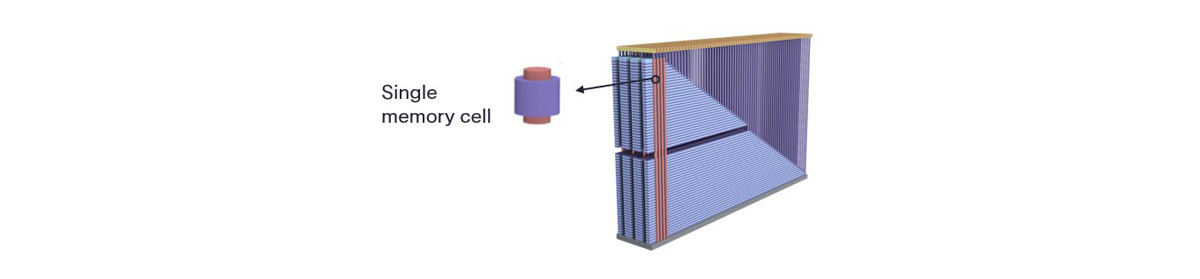

3次元への移行は10年前にNAND型フラッシュメモリにも起こり、それまで水平だったメモリビットの列は垂直方向へと積み重なるようになりました。

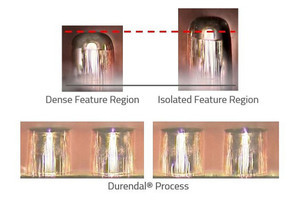

材料の薄い層が交互に垂直に積み上げられて構成されており、製造工程では可能な限り多くの層を積み重ねます。製造の際には、少なくとも2つの点で非常に慎重な作業が要求されます。まず、各層は、層の各ビットが他のビットと同じ寸法になるように厚みが均一で完全に平坦でなければなりません。次に、層は相互に接続されていなければなりません。これは、まず層を積み重ね、これを貫通するようにエッチングで穴を開け、その穴に適切な接続材料を充填することで実現します。この2つは非常に難しいエッチング作業および成膜作業であり、正確さが要求されます。

これらの課題により、積み重ねられる層の数は限られており、層を増やすには新たなアプローチが必要になります。

将来を見据えて:3D DRAM

DRAMは、3D NANDとは物理的に全く異なる仕組みに基づいており、全く別のアプローチを要します。

DRAMには背の高いコンデンサが必要ですが、これを2Dアレイで精密に組み立てることは困難です。また、これらを垂直に積み上げることはいっそう困難で、誘電体や活性シリコンを積層する経済的な方法を探るためには、さらなる開発が必要です。リソグラフィは一度に複数の層に作用することが必要な可能性があり、量産可能なプロセスは、まだ存在しません。

3Dパッケージングの導入が加速

チップは、プリント基板(PCB)に搭載するためにパッケージ化されています。過去にはパッケージは、デリケートなシリコンチップを保護し、基板に接続するための手段にすぎませんでした。現在では、パッケージは複数のチップを保持することが多くなり、フットプリントを縮小する必要から3D化が進んでいます。

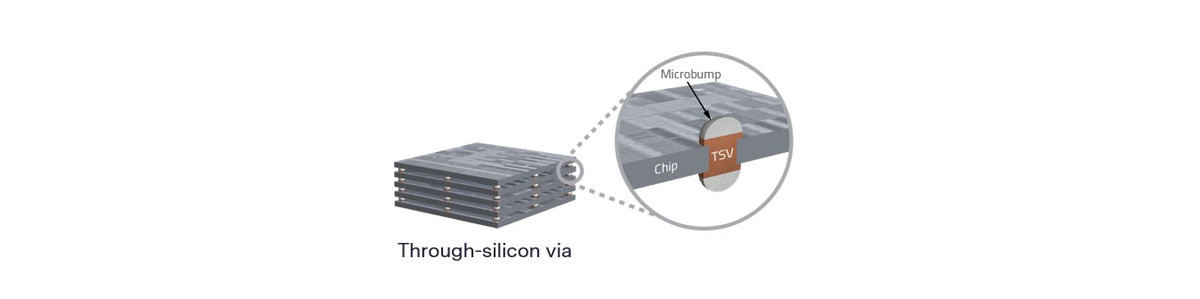

3Dパッケージではチップを積み重ねる必要があり、チップ同士を高密度に接続しなければなりません。このような接続では、距離が非常に短く、一度により多くの信号を転送できるため、信号速度の向上が可能です。ただし、2つ以上のチップを積み重ねた場合、信号の一部は伝導チャネルを通って移動し、上方に積まれたチップにつながる必要があります。このチャネルはシリコン貫通電極(TSV)と呼ばれます。

エンドマーケットでのチップの3D積層で注目すべき用途はメモリであり、最もよく知られた例は高帯域幅メモリ(HBM)です。また、CPUなどのロジックチップにメモリチップを積層することも可能で、それによりメモリからのデータ取得が高速化されます。

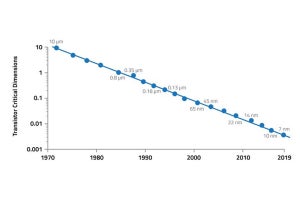

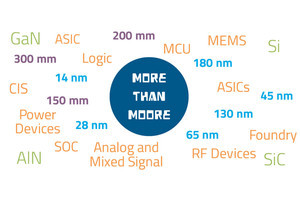

スケーリングに必須な3D

半導体製造におけるあらゆるスケーリングの限界に対応するために3Dを検討することは、今や標準的な慣行となっています。3Dはすべての問題を解決する選択肢とはいえないまでも、上記のような用途では特に有効です。 新しい用途が見つかるたびに、どうしたらそれを形成できるかという問題が発生します。チップ業界の3Dへの転換を可能にする主要な原動力として半導体製造装置を位置付ける、シリコン処理の革新的な考え方と継続的な開発が求められます。